## HDL Verifier™ User's Guide

# MATLAB&SIMULINK®

R

**R**2020**a**

### **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\searrow$

508-647-7000

#### The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

HDL Verifier<sup>™</sup> User's Guide

© COPYRIGHT 2003-2020 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

Screenshots of ModelSim in theHDL Verifier<sup>™</sup> documentation are copyright protected by Mentor Graphics Corporation.

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See

www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ {\tt products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ {\tt see\ www.mathworks.com/patents\ for\ more\ information.}$

#### **Revision History**

August 2003 February 2004 June 2004 October 2004 December 2004 March 2005 September 2005 March 2006 September 2006 March 2007 September 2007 March 2008 October 2008 March 2009 September 2009 March 2010 September 2010 April 2011 September 2011 March 2012 September 2012 March 2013 September 2013 March 2014 October 2014 September 2015 March 2016 September 2016 March 2017 September 2017 March 2018 September 2018 March 2019 September 2019 March 2020

Online only Online only

New for Version 1 (Release 13SP1) Revised for Version 1.1 (Release 13SP1) Revised for Version 1.1.1 (Release 14) Revised for Version 1.2 (Release 14SP1) Revised for Version 1.3 (Release 14SP1+) Revised for Version 1.3.1 (Release 14SP2) Revised for Version 1.4 (Release 14SP3) Revised for Version 2.0 (Release 2006a) Revised for Version 2.1 (Release 2006b) Revised for Version 2.2 (Release 2007a) Revised for Version 2.3 (Release 2007b) Revised for Version 2.4 (Release 2008a) Revised for Version 2.5 (Release 2008b) Revised for Version 2.6 (Release 2009a) Revised for Version 3.0 (Release 2009b) Revised for Version 3.1 (Release 2010a) Revised for Version 3.2 (Release 2010b) Revised for Version 3.3 (Release 2011a) Revised for Version 3.4 (Release 2011b) Revised for Version 4.0 (Release 2012a) Revised for Version 4.1 (Release 2012b) Revised for Version 4.2 (Release 2013a) Revised for Version 4.3 (Release 2013b) Revised for Version 4.4 (Release 2014a) Revised for Version 4.5 (Release 2014b) Revised for Version 4.7 (Release 2015b) Revised for Version 5.0 (Release 2016a) Revised for Version 5.1 (Release 2016b) Revised for Version 5.2 (Release 2017a) Revised for Version 5.3 (Release 2017b) Revised for Version 5.4 (Release 2018a) Revised for Version 5.5 (Release 2018b) Revised for Version 5.6 (Release 2019a) Revised for Version 6.0 (Release 2019b) Revised for Version 6.1 (Release 2020a)

## Contents

#### **HDL Verification with Cosimulation**

1

2

## Setup and Run Cosimulation for MATLAB

| Start MATLAB Server       1         Start HDL Simulator       1                                                                                                                                                                                             | L-2<br>L-2<br>L-2<br>L-3               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Process for Running MATLAB Cosimulation       1         Check MATLAB Cosimulation Server's Link Status       1         Run Cosimulation       1         Apply Stimuli to Cosimulation Session with force Command       1         Restart Simulation       1 | L-4<br>L-4<br>L-4<br>L-7<br>L-8<br>L-8 |

## HDL Cosimulation Using MATLAB Test Bench Function

| Create a MATLAB Test Bench                           | 2-2  |

|------------------------------------------------------|------|

| Write HDL Modules for MATLAB Test Bench              | 2-3  |

| Write a Test Bench Function                          | 2-6  |

| Set Up Cosimulation Test Bench                       | 2-13 |

| Place Test Bench on MATLAB Search Path               | 2-13 |

| Bind Test Bench Function Calls With matlabtb         | 2-13 |

| Schedule Options for a Test Bench Session            | 2-16 |

| Verify HDL Module with MATLAB Test Bench             | 2-18 |

| Tutorial Overview                                    | 2-18 |

| Set Up Tutorial Files                                | 2-18 |

| Start the MATLAB Server                              | 2-19 |

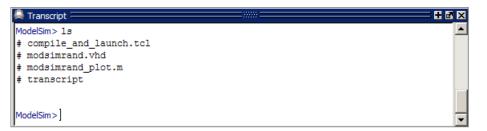

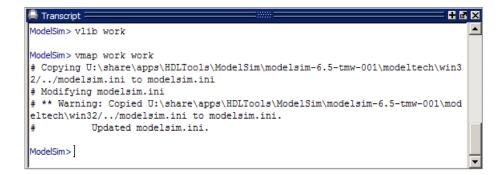

| Start ModelSim Simulator and Set Up for Cosimulation | 2-20 |

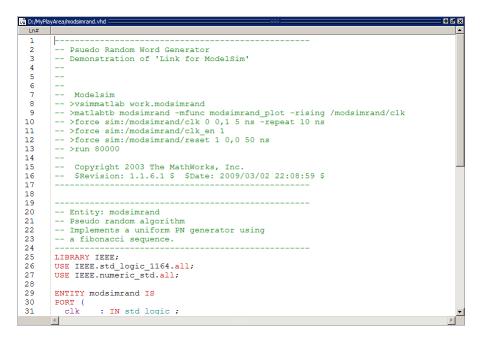

| Develop VHDL Code                                    | 2-21 |

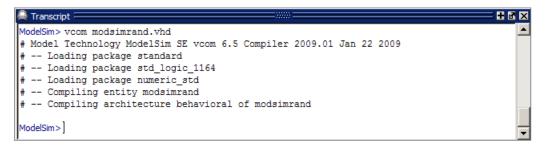

| Compile VHDL Code                                    | 2-23 |

| Develop MATLAB Function                              | 2-23 |

| Load Simulation                                      | 2-24 |

| Run Simulation                                       | 2-26 |

| Shut Down Simulation                                 | 2-29 |

## HDL Cosimulation Using MATLAB Component Function

3

4

5

6

| Create a MATLAB Component Function                                                                                                                                         | 3-2<br>3-3<br>3-6 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Set Up Cosimulation Component<br>Place Component Function on MATLAB Search Path<br>Bind Component Function Calls With matlabcp<br>Schedule Options for a Component Session | 3-8               |

#### HDL Cosimulation Using MATLAB System Object

| Create a MATLAB System Object | 4 | <b>-</b> 2 |

|-------------------------------|---|------------|

|-------------------------------|---|------------|

#### Set Up and Run Simulation for Simulink

| Start HDL Simulator for Cosimulation in SimulinkStart HDL Simulator from MATLABLoad Instance of HDL Module for Cosimulation                                            | 5-2<br>5-2<br>5-2        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Run a Simulink Cosimulation Session         Set Simulink Model Configuration Parameters         Determine Available Socket Port Number         Check Connection Status | 5-4<br>5-4<br>5-4<br>5-4 |

| Run and Test Cosimulation ModelSet Parameters from a Tcl ScriptAvoid Race Conditions in HDL Simulation with Test Bench                                                 | 5-4<br>5-5<br>5-7        |

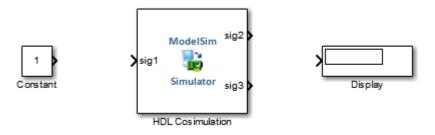

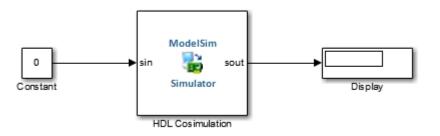

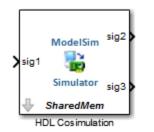

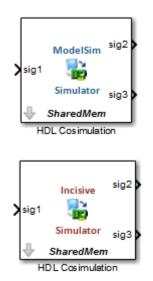

| Cosimulation and the HDL Verifier HDL Cosimulation Block                                                                                                               | 5-8                      |

#### Simulink Test Bench for HDL Component

## Simulink as a Test Bench6-2Communications During Test Bench Cosimulation6-2HDL Cosimulation Block Features for Test Bench Simulation6-4

| Create a Simulink Cosimulation Test Bench                    |   |

|--------------------------------------------------------------|---|

| Configure HDL Cosimulation Block Interface                   |   |

| Verify HDL Module with Simulink Test Bench                   | ( |

| Tutorial Overview                                            | ( |

| Develop VHDL Code                                            | ( |

| Compile VHDL Code                                            | ( |

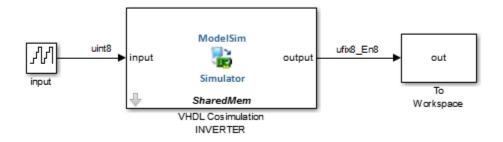

| Create Simulink Model                                        | ( |

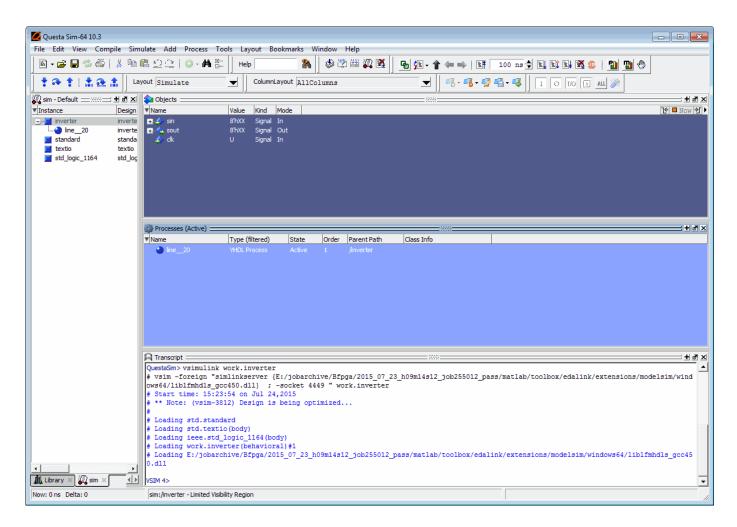

| Set Up ModelSim for Use with Simulink                        | ( |

| Load Instances of VHDL Entity for Cosimulation with Simulink | ( |

| Run Simulation                                               | ( |

| Shut Down Simulation                                         | ( |

## **Replace HDL Component with Simulink Algorithm**

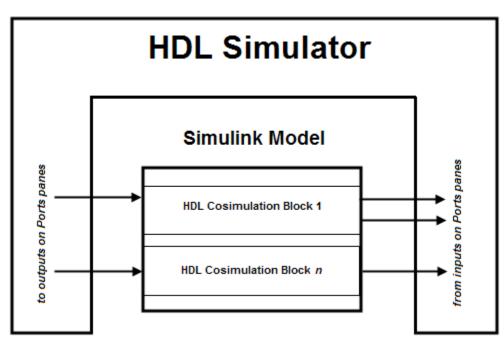

| Component Simulation with Simulink                            | 7-2 |

|---------------------------------------------------------------|-----|

| How the HDL Simulator and Simulink Software Communicate Using |     |

| HDL Verifier For Component Simulation                         | 7-2 |

| HDL Cosimulation Block Features for Component Simulation      | 7-3 |

| Create Simulink Model for Component Cosimulation              | 7-5 |

| Code an HDL Component                                         | 7-5 |

| Define HDL Cosimulation Block Interface                       | 7-7 |

## Record Simulink Signal State Transitions for Post-Processing

## 8

7

| Add a Value Change Dump (VCD) FileIntroduction to the To VCD File BlockUsing the To VCD File Block | 8-2 |

|----------------------------------------------------------------------------------------------------|-----|

| Visually Compare Simulink Signals with HDL Signals                                                 | 8-5 |

| Tutorial: Overview                                                                                 | 8-5 |

| Tutorial: Instructions                                                                             | 8-5 |

## **HDL Code Import for Cosimulation**

## 9

| Prepare to Import HDL Code for Cosimulation | 9-2 |

|---------------------------------------------|-----|

| HDL Code Import Features                    | 9-2 |

| HDL Code Import Workflows                   | 9-3 |

| Cosimulation Wizard Navigation                                   | 9-3<br>9-3                 |

|------------------------------------------------------------------|----------------------------|

| Import HDL Code for MATLAB Function                              | 9-4                        |

| Cosimulation Type—MATLAB Function                                | 9-4                        |

| HDL Files—MATLAB Function                                        | 9- <del>4</del><br>9-5     |

| IDL FIRES-MATLAD FUNCTION                                        | 9-5<br>9-6                 |

| HDL Compilation—MATLAB Function                                  |                            |

| HDL Modules—MATLAB Function                                      | 9-7                        |

| Callback Schedule—MATLAB Function                                | 9-8                        |

| Script Generation—MATLAB Function                                | 9-9                        |

| Complete the Component or Test Bench Function                    | 9-10                       |

| Import HDL Code for MATLAB System Object                         | 9-12                       |

| Cosimulation Type—MATLAB System Object                           | 9-12                       |

| HDL Files—MATLAB System Object                                   | 9-14                       |

| HDL Compilation—MATLAB System Object                             | 9-15                       |

| Simulation Options—MATLAB System Object                          | 9-16                       |

| Input/Output Ports—MATLAB System Object                          | 9-17                       |

|                                                                  | 9-17<br>9-18               |

| Output Port Details—MATLAB System Object                         |                            |

| Clock/Reset Details—MATLAB System Object                         | 9-19                       |

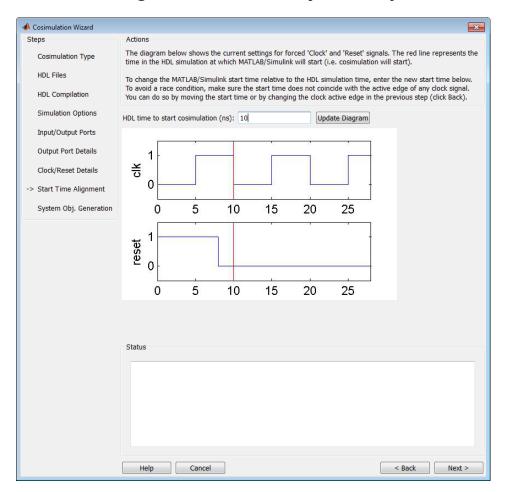

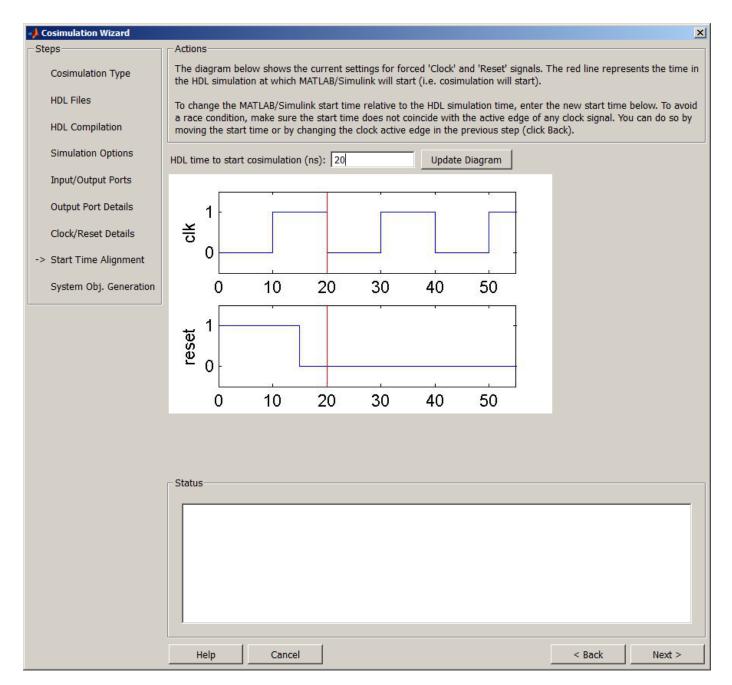

| Start Time Alignment—MATLAB System Object                        | 9-20                       |

| System Object Generation                                         | 9-21                       |

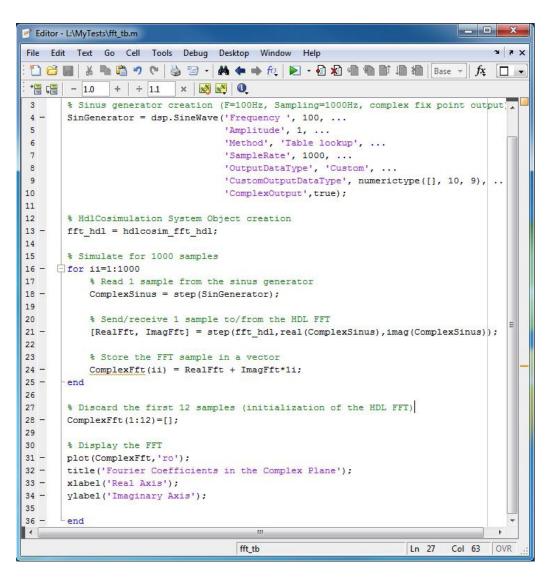

| Write System Object Test Bench                                   | 9-21                       |

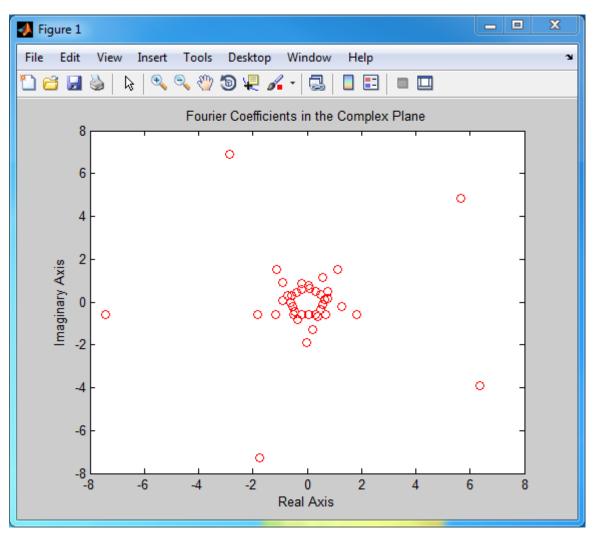

| Run Cosimulation and Verify HDL Design                           | 9-22                       |

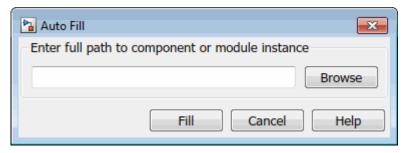

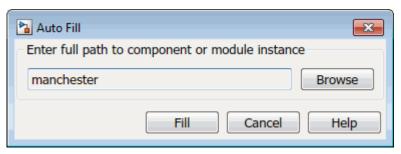

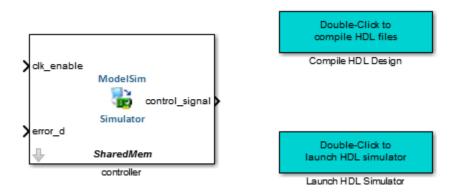

| Import HDL Code for HDL Cosimulation Block                       | 9-23                       |

| Cosimulation Type—Simulink Block                                 | 9-23                       |

| HDL Files—Simulink Block                                         | 9-24                       |

| HDL Compilation—Simulink Block                                   | 9-25                       |

| Simulation Options—Simulink Block                                | 9-26                       |

| Input/Output Ports—Simulink Block                                | 9-27                       |

| Output Port Details—Simulink Block                               | 9-28                       |

|                                                                  | 9-20                       |

| Clock/Reset Details—Simulink Block                               |                            |

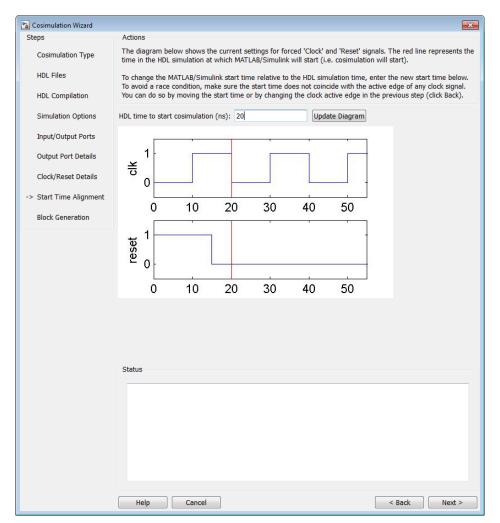

| Start Time Alignment—Simulink Block                              | 9-30                       |

| Generate Block                                                   | 9-31                       |

| Complete Simulink Model                                          | 9-31                       |

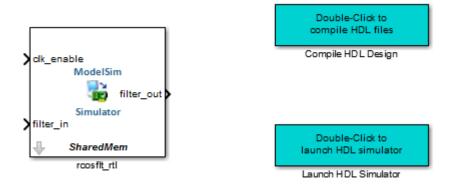

| Performing Cosimulation                                          | 9-33                       |

|                                                                  |                            |

| Cosimulation Wizard for MATLAB System Object                     | 9-34                       |

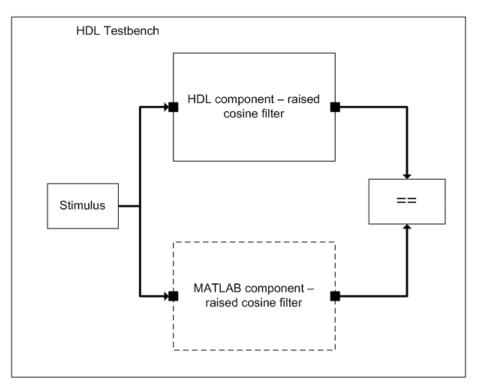

| Verify Raised Cosine Filter Design Using MATLAB                  | 9-46                       |

| MATLAB and Cosimulation Wizard Tutorial Overview                 | <b>9-40</b>                |

|                                                                  | <b>9-40</b><br><b>9-47</b> |

| Tutorial: Set Up Tutorial Files (MATLAB)                         | -                          |

| Tutorial: Launch Cosimulation Wizard (MATLAB)                    | 9-47                       |

| Tutorial: Configure the Component Function with the Cosimulation |                            |

| Wizard                                                           | 9-47                       |

| Tutorial: Customize Callback Function                            | 9-53                       |

| Tutorial: Run Cosimulation and Verify HDL Design                 | 9-56                       |

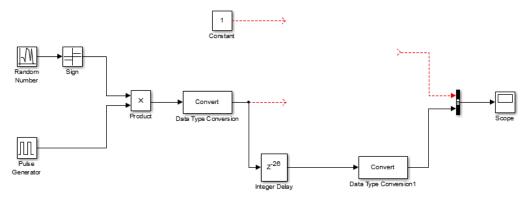

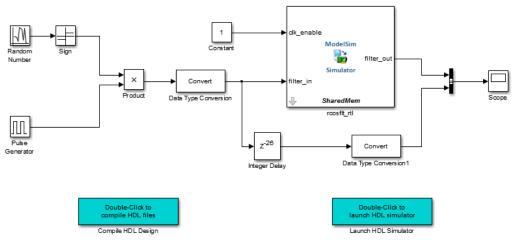

| Verify Raised Cosine Filter Design Using Simulink                | 9-58                       |

| Simulink and Cosimulation Wizard Tutorial Overview               | 9-58                       |

| Tutorial: Set Up Tutorial Files (Simulink)                       | 9-58                       |

| Tutorial: Launch Cosimulation Wizard (Simulink)                  | 9-59                       |

|                                                                  |                            |

| Tutorial: Configure the HDL Cosimulation Block with the Cosimulation |      |

|----------------------------------------------------------------------|------|

| Wizard                                                               | 9-59 |

| Tutorial: Create Test Bench to Verify HDL Design                     | 9-68 |

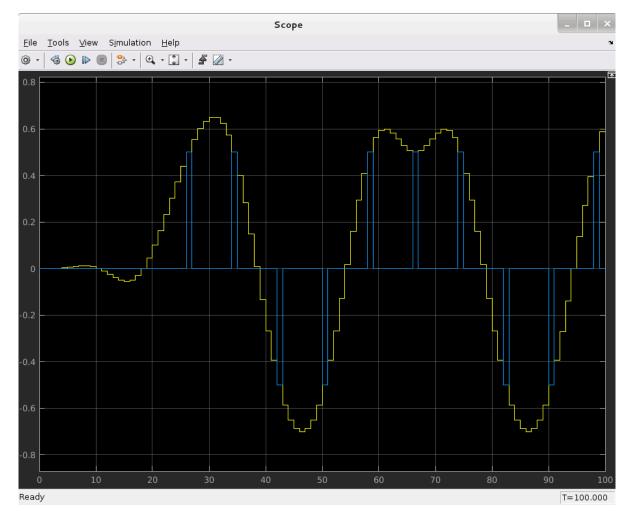

| Tutorial: Run Cosimulation and Verify HDL Design                     | 9-70 |

| Help Button                                                          | 9-73 |

| Cosimulation Type                                                    | 9-73 |

| HDL Files                                                            | 9-74 |

| HDL Compilation                                                      | 9-75 |

| HDL Modules                                                          | 9-76 |

## 10

## HDL Cosimulation Guide

| Set Up for HDL Cosimulation<br>Cosimulation Configurations<br>HDL Simulator Startup                                                                                                                                              | 10-2<br>10-2<br>10-4                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Cosimulation Libraries       Set Up Configuration and Run Diagnostics                                                                                                                                                            | 10-4<br>10-7<br>10-10                              |

| Cross-Network Cosimulation                                                                                                                                                                                                       | 10-16<br>10-16<br>10-16                            |

| Performing Cross-Network Cosimulation Using MATLAB<br>Performing Cross-Network Cosimulation Using Simulink                                                                                                                       | 10-10<br>10-17<br>10-18                            |

| Test Bench and Component Function Writing<br>Writing Functions Using the HDL Instance Object                                                                                                                                     | 10-21<br>10-21                                     |

| Writing Functions Using Port Information         Simulation Speed Improvement Tips                                                                                                                                               | 10-24<br>10-28                                     |

| Obtaining Baseline Performance Numbers          Analyzing Simulation Performance          Cosimulating Frame-Based Signals with Simulink                                                                                         | 10-28<br>10-28<br>10-29                            |

| Race Conditions in HDL Simulators         Avoiding Race Conditions         Potential Race Conditions in Simulink Cosimulation Sessions         Potential Race Conditions in MATLAB Cosimulation Sessions         Further Reading | 10-35<br>10-35<br>10-35<br>10-36<br>10-36          |

| Supported Data Types                                                                                                                                                                                                             | 10-37<br>10-37<br>10-39<br>10-39<br>10-40<br>10-41 |

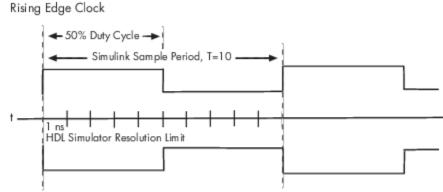

| Simulation Timescales<br>Overview to the Representation of Simulation Time<br>Defining the Simulink and HDL Simulator Timing Relationship<br>Setting the Timing Mode with HDL Verifier                                           | 10-45<br>10-45<br>10-46<br>10-46                   |

| Specify Timing Relationship Automatically                | <b>10-4</b> 7 |

|----------------------------------------------------------|---------------|

| Relative Timing Mode                                     | 10-49         |

| Absolute Timing Mode                                     | 10-52         |

| Timing Mode Usage Considerations                         | 10-54         |

| Setting HDL Cosimulation Block Port Sample Times         | 10-55         |

| Clock, Reset, and Enable Signals                         | 10-56         |

| Driving Clocks, Resets, and Enables                      | 10-56         |

| Adding Signals Using Simulink Blocks                     | 10-56         |

| Creating Optional Clocks with the Clocks Pane of the HDL |               |

| Cosimulation Block                                       | 10-57         |

| Driving Signals by Adding Force Commands                 | 10-59         |

| TCD/ID Socket Dorts                                      | 10-62         |

| TCP/IP Socket Ports                                      | 10-02         |

## FPGA-in-the-Loop

## About FPGA-in-the-Loop Simulation

## 11

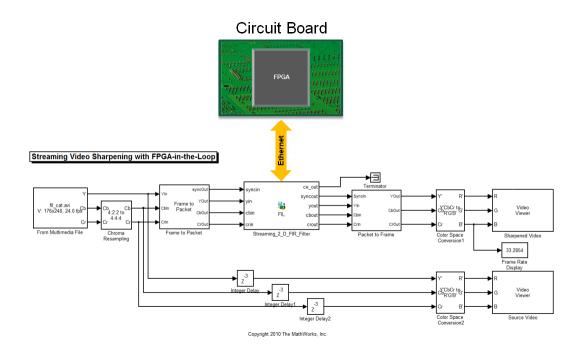

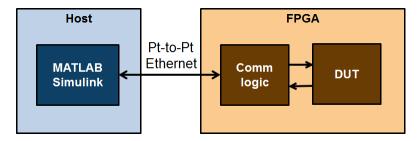

| FPGA-in-the-Loop Simulation          | 11-2 |

|--------------------------------------|------|

| What is FPGA-in-the-Loop Simulation? | 11-2 |

| What You Need To Know                | 11-4 |

## **Prepare FPGA Connection**

## 12

| FPGA-in-the-Loop Simulation Workflows                    | 12-2  |

|----------------------------------------------------------|-------|

| Download FPGA Board Support Package                      | 12-3  |

| HDL Verifier Support Packages for FPGA Boards            | 12-3  |

| Install with Connection to Internet                      | 12-4  |

| Install Support Package Offline                          | 12-5  |

| Set Up FPGA Design Software Tools                        | 12-6  |

| Xilinx Software                                          | 12-6  |

| Intel Software                                           | 12-6  |

| Microsemi Software                                       | 12-6  |

| Guided Hardware Setup                                    | 12-7  |

| Select Board and Interface for Use with FPGA-in-the-Loop | 12-7  |

| Connection Requirements                                  | 12-7  |

| Connection Setup                                         | 12-8  |

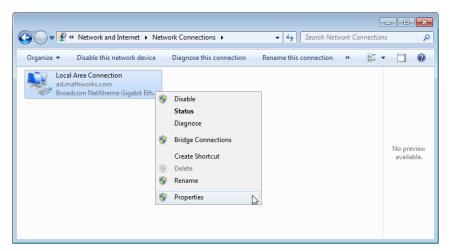

| Configure Network Card on Host                           | 12-11 |

| PCI Express Driver Installation                          | 12-11 |

| Verify Setup                                             | 12-11 |

| Open the Example                                                                                                                                                                     | 12-11                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

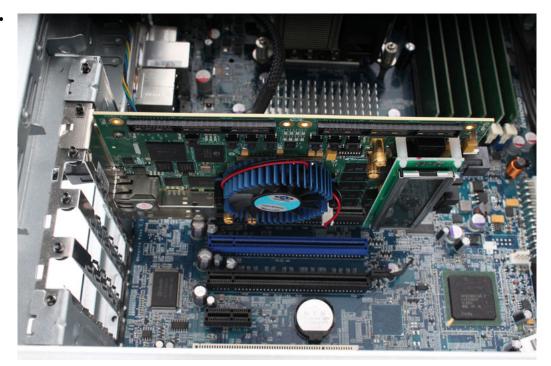

| Manual Hardware Setup          Step 1. Set Up FPGA Development Board          Step 2. Set Up Board Connection                                                                        | 12-13<br>12-13<br>12-14          |

| Prepare DUT For FIL Interface Generation         Files and Information Required for FIL Generation         Apply FIL System Object Requirements         Apply FIL Block Requirements | 12-18<br>12-18<br>12-18<br>12-21 |

## **FIL Interface Generation and Simulation**

## 13

| Block Generation with the FIL Wizard                        | 13-2  |

|-------------------------------------------------------------|-------|

| Step 1: Set Up FPGA Design Software Tools                   | 13-2  |

| Step 2: Start FIL Wizard                                    | 13-3  |

| Step 3: Set FIL Options for FIL Block                       | 13-3  |

| Step 4: Add HDL Source Files for FIL Block                  | 13-5  |

| Step 5: Verify DUT I/O Ports for FIL Block                  | 13-6  |

| Step 6: Specify Output Types for FIL Block                  | 13-7  |

| Step 7: Specify Build Options for FIL Block                 | 13-8  |

| Step 8: Initiate Build                                      | 13-8  |

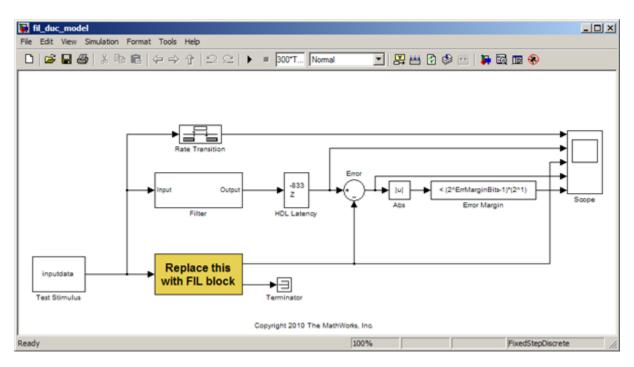

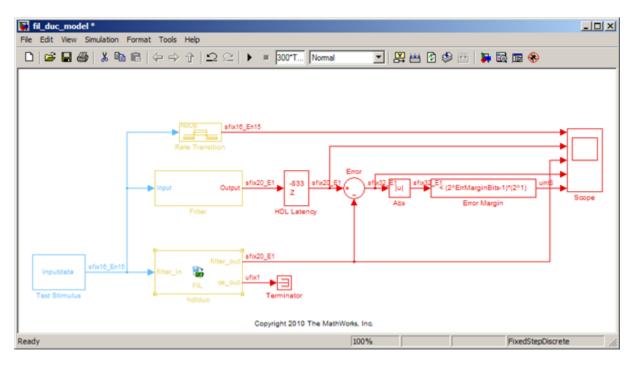

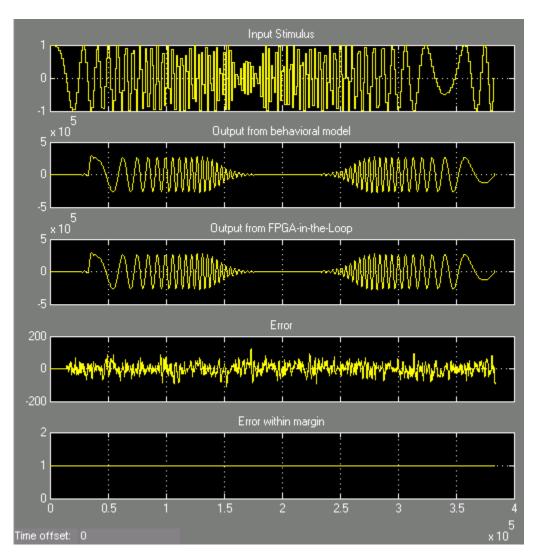

| Step 9: Integrate and Simulate                              | 13-9  |

| System Object Generation with the FIL Wizard                | 13-12 |

| Step 1: Set Up FPGA Design Software Tools                   | 13-12 |

| Step 2: Start FIL Wizard                                    | 13-13 |

| Step 3: Set FIL Options for System Object                   | 13-13 |

| Step 4: Add HDL Source Files for System Object              | 13-15 |

| Step 5: Verify DUT I/O Ports for System Object              | 13-16 |

| Step 6: Specify Output Types for System Object              | 13-17 |

| Step 7: Specify Build Options for System Object             | 13-18 |

|                                                             |       |

| Step 8: Initiate Build       Step 9: Integrate and Simulate | 13-18 |

## FIL Using HDL Coder HDL Workflow Advisor

## 14

| FIL Simulation with HDL Workflow Advisor for Simulink       | 14-2 |

|-------------------------------------------------------------|------|

| Step 1: Start HDL Workflow Advisor                          | 14-2 |

| Step 2: Set Target and Target Frequency                     | 14-2 |

| Step 3: Prepare Model for HDL Code Generation               | 14-3 |

| Step 4: HDL Code Generation                                 | 14-3 |

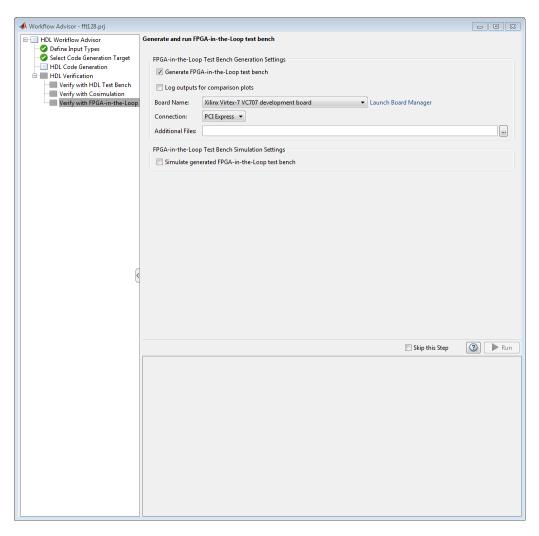

| Step 5: Set FPGA-in-the-Loop Options                        | 14-3 |

| Step 6: Generate FPGA Programming File and FPGA-in-the-Loop |      |

| Model                                                       | 14-6 |

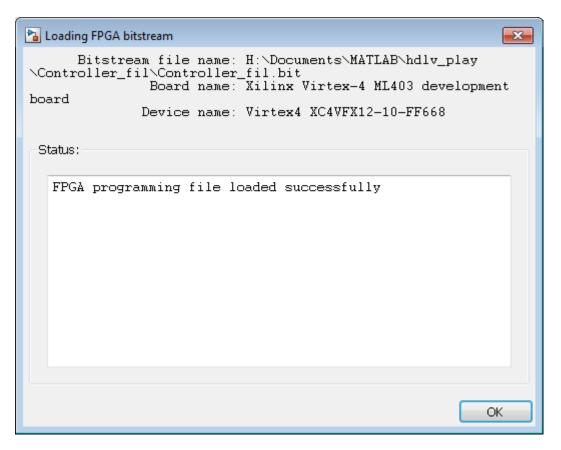

| Step 7: Load Programming File onto FPGA                     | 14-7 |

| Step 8: Run Simulation                                      | 14-7 |

| FIL Simulation with HDL Workflow Advisor for MATLAB       | 14-8  |

|-----------------------------------------------------------|-------|

| Step 1: Start HDL Workflow Advisor                        | 14-8  |

| Step 2: Select Target                                     | 14-8  |

| Step 3: Select Workflow                                   | 14-8  |

| Step 4: Select FPGA-in-the-Loop Options                   | 14-8  |

| Step 5: Generate FPGA Programming File and Run Simulation | 14-12 |

## **Troubleshooting FPGA-in-the-Loop**

| Troubleshooting FIL | 15-2 |

|---------------------|------|

#### **FIL Examples**

17-19

17-20

## **16**

17

15

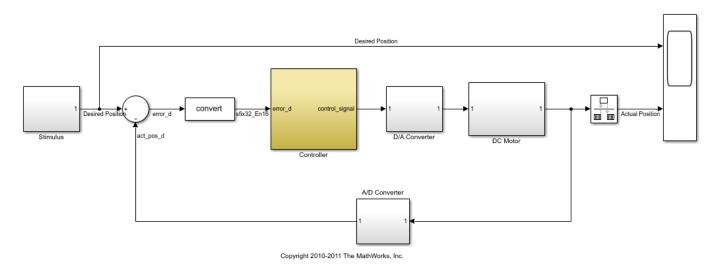

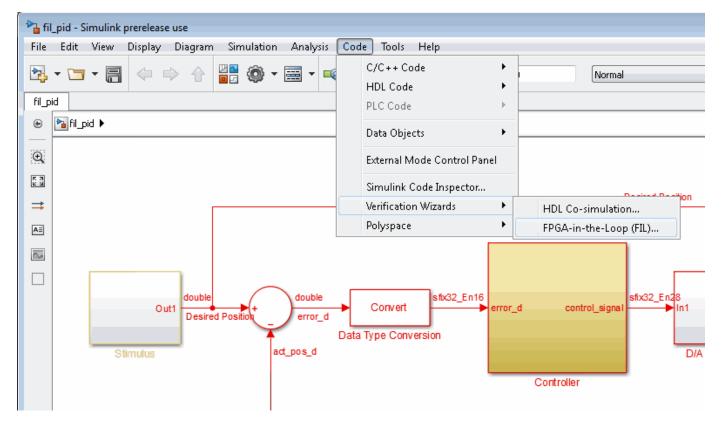

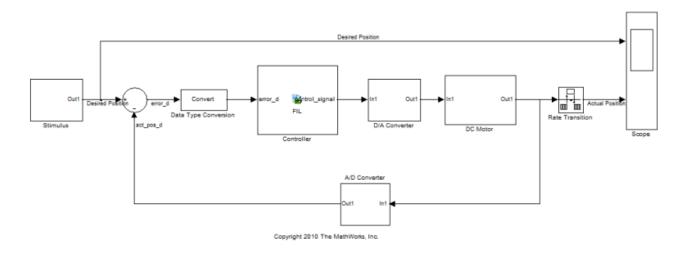

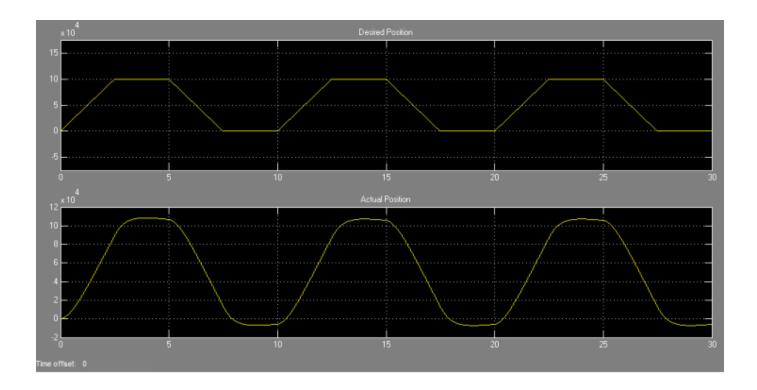

| Verify HDL Implementation of PID Controller Using FPGA-in-the-<br>Loop | 16-2  |

|------------------------------------------------------------------------|-------|

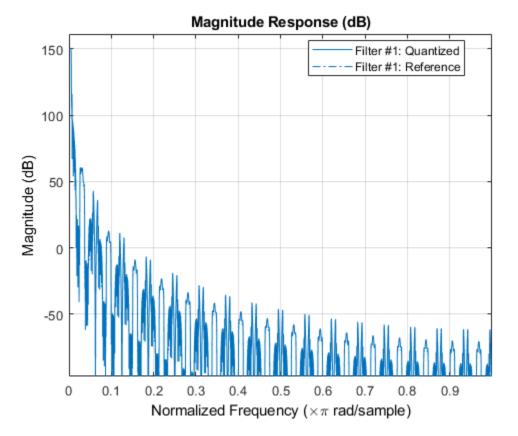

| Verify Digital Up-Converter Using FPGA-in-the-Loop                     | 16-19 |

## **FPGA Board Customization**

| Feature Description                                  | 1        |

|------------------------------------------------------|----------|

| Custom Board Management                              | 1        |

| FPGA Board Requirements                              |          |

| Create Custom FPGA Board Definition                  | 1        |

| Create Xilinx KC705 Evaluation Board Definition File | . 1      |

| Overview                                             | 1        |

| What You Need to Know Before Starting                | . 1      |

| Start New FPGA Board Wizard                          | . 1      |

| Provide Basic Board Information                      | 1        |

| Specify FPGA Interface Information                   | 1        |

| Enter FPGA Pin Numbers                               | 17       |

| Run Optional Validation Tests                        | 17       |

| Save Board Definition File                           | 17       |

| Use New FPGA Board                                   | 17       |

|                                                      |          |

| FPGA Board Manager                                   | 17       |

| FPGA Board Manager                                   | 17<br>17 |

Search .....

FIL Enabled/Turnkey Enabled .....

| Create Custom Board   | 17-20 |

|-----------------------|-------|

| Add Board from File   | 17-20 |

| Get More Boards       | 17-20 |

| View/Edit             | 17-20 |

| Remove                | 17-20 |

| Clone                 | 17-20 |

| Validate              | 17-20 |

| New FPGA Board Wizard | 17-21 |

| Basic Information     | 17-22 |

| Interfaces            | 17-22 |

| FIL I/O               | 17-25 |

| Turnkey I/O           | 17-27 |

| Validation            | 17-30 |

| Finish                | 17-31 |

| FPGA Board Editor     | 17-32 |

| General Tab           | 17-32 |

| Interface Tab         | 17-34 |

### **FPGA Data Capture**

| 18 |  |

|----|--|

|----|--|

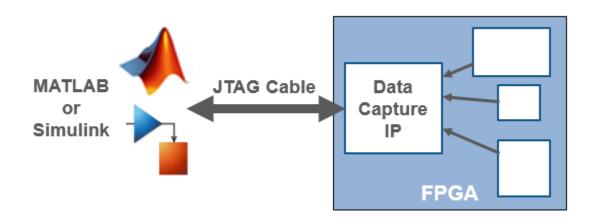

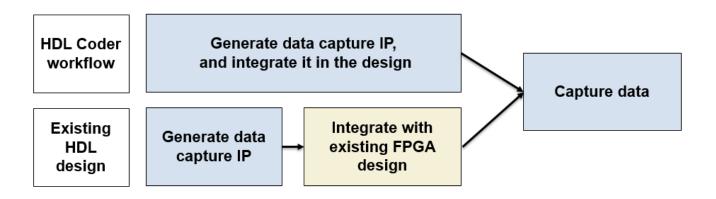

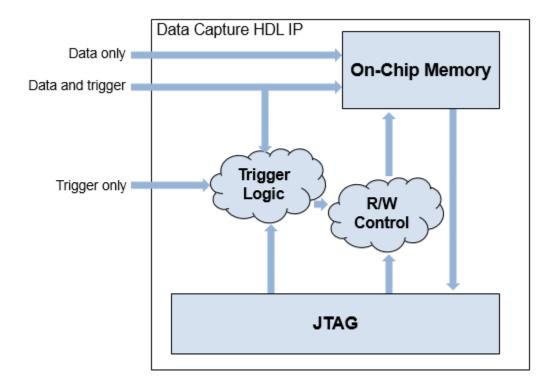

| Data Capture Workflow                                                               | 18-2                         |

|-------------------------------------------------------------------------------------|------------------------------|

| Configure and Generate IP Core for an Existing HDL Design<br>Integrate IP into FPGA | 18-3<br>18-3<br>18-4<br>18-4 |

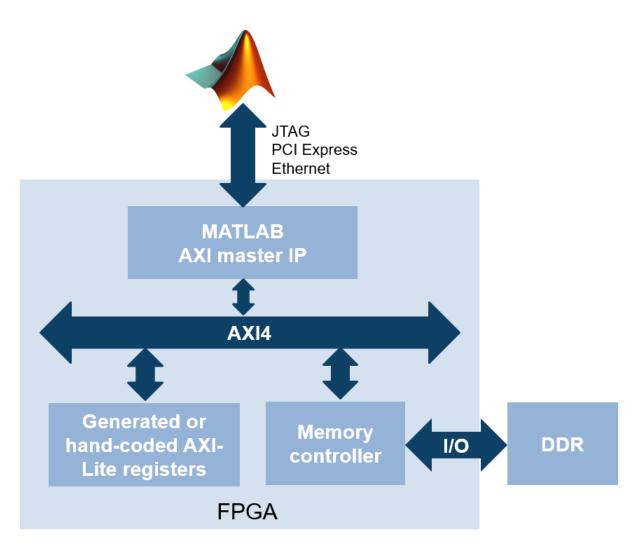

#### **MATLAB AXI Master**

## **19**

| Set Up for MATLAB AXI Master | 19-2 |

|------------------------------|------|

| JTAG Considerations          | 19-3 |

## SystemC TLM Generation

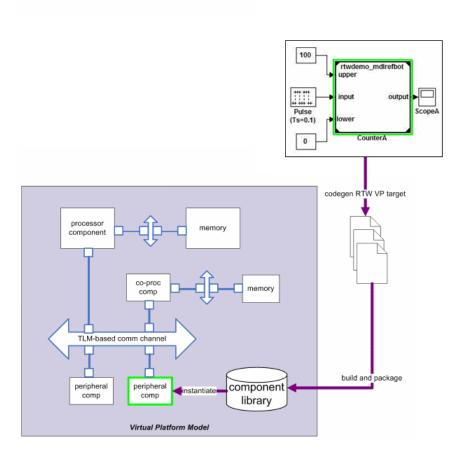

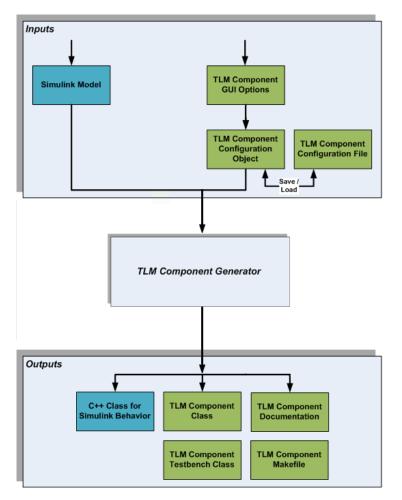

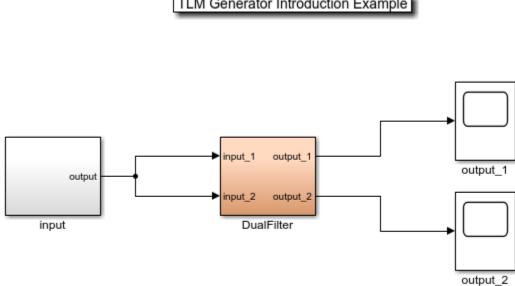

How TLM Component Generation Works

20

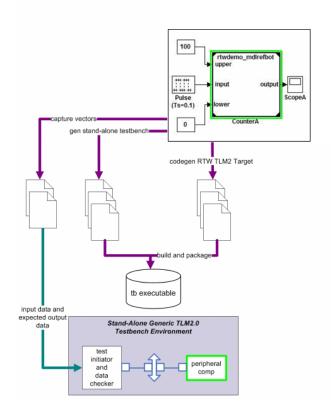

TLM Generation Algorithms

20-2

| The TLM Generation Process | 20-3 |

|----------------------------|------|

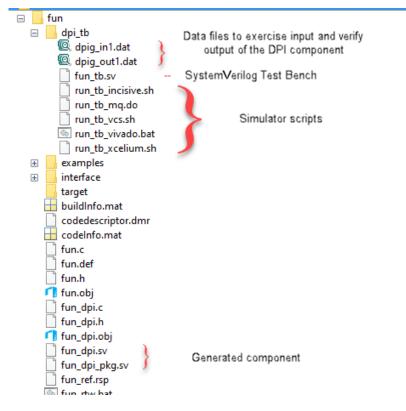

| Generated TLM Files        | 20-5 |

## **TLM Component Architecture**

## 21

22

23

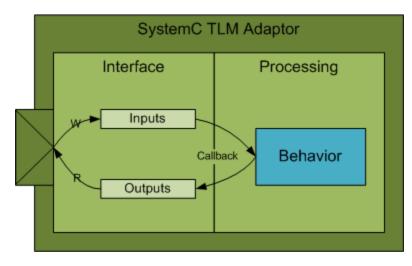

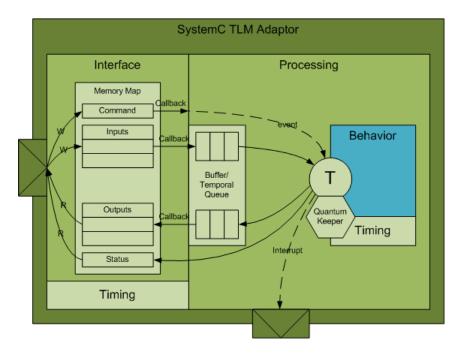

| TLM Component Architecture     |       |

|--------------------------------|-------|

| Overview of Component Features | 21-2  |

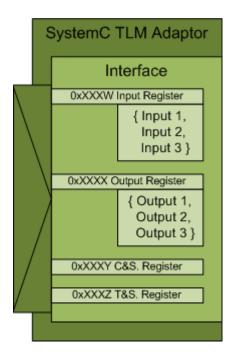

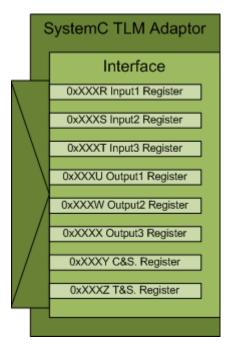

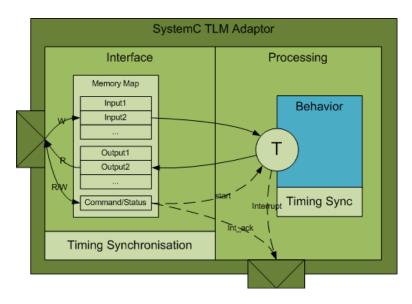

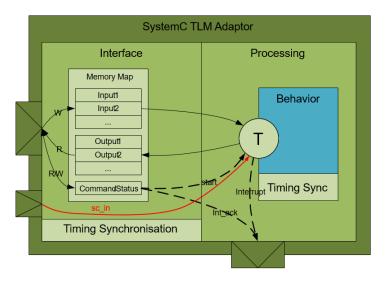

| Memory Mapping                 | 21-3  |

| Command and Status Register    |       |

| Interrupt                      | 21-11 |

| Test and Set Register          | 21-11 |

| Registers and Signal Ports     | 21-11 |

## **Getting Started with TLM Component Generation**

| Getting Started with TLM Generator | <br>22-2 |

|------------------------------------|----------|

#### **Generate TLM Component**

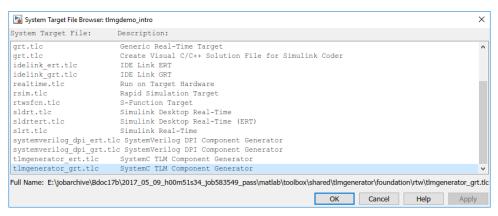

| TLM Component Generation Workflow    | 23-2                 |

|--------------------------------------|----------------------|

| Subsystem Guidelines and Limitations | 23-3                 |

| Select TLM Generator System Target   | 23-4                 |

| Select TLM Mapping Options           | 23-6<br>23-6<br>23-7 |

| Select TLM Processing Options        | 23-8<br>23-8<br>23-8 |

| Select TLM Timing Options            | 23-9                 |

| Select TLM Test Bench Options        | 23-10                |

| Select TLM Compilation Options       | 23-12                |

| Generate Component and Test Bench    | 23-15                |

#### **xiv** Contents

| Prepare IP-XACT File for Import                 | 23-16 |

|-------------------------------------------------|-------|

| Required Information for Imported IP-XACT Files | 23-16 |

| Bus Interface Definition with No Memory Map     | 23-17 |

| Bus Interface Definition with Memory Mapping    | 23-18 |

| Mapping to a Signal Port                        | 23-21 |

| Contents of Generated IP-XACT File              | 23-24 |

| Overview of Generated IP-XACT File              | 23-24 |

| Generated Simulink Mapping                      | 23-24 |

| Generated Simulink Mapping in Memory Map        | 23-25 |

| Generated Metadata                              | 23-26 |

| Implement Memory Map with SCML                  | 23-28 |

| What Is SCML?                                   | 23-28 |

| Workflow                                        | 23-28 |

| Generated Code                                  | 23-28 |

## **Run TLM Component Test Bench**

## 24

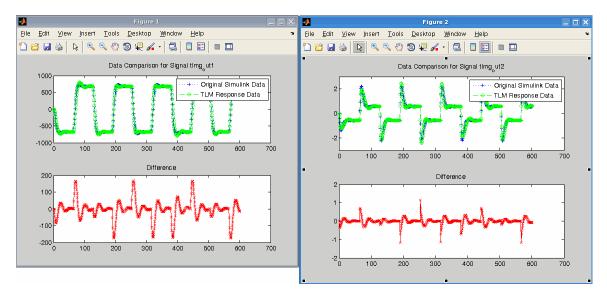

| Testing TLM Components                                  | 24-2 |

|---------------------------------------------------------|------|

| TLM Component Test Bench Overview                       | 24-2 |

| TLM Component Compilation                               | 24-2 |

| Automatic Verification of the Generated Component       | 24-2 |

| Report Generation                                       | 24-3 |

| Working with Configurations                             | 24-3 |

| Considerations When Creating a TLM Component Test Bench | 24-3 |

| Run TLM Component Test Bench                            | 24-5 |

#### **Export TLM Component to SystemC Environment**

## 25

| Export TLM Component                            | 25-2 |

|-------------------------------------------------|------|

| Identify Generated Files                        | 25-2 |

| Create Static Library with TLM Component        | 25-3 |

| Create Standalone Executable with TLM Component | 25-4 |

| TLM Component Constructor                       | 25-6 |

## Configuration Parameters for TLM Generator Target

## 26

| TLM Component Generation | 26-2 |

|--------------------------|------|

| TLM Mapping              | 26-2 |

| TLM Processing           | 26-7 |

| TLM Timing      | 26-8  |

|-----------------|-------|

| TLM Testbench   |       |

| TLM Compilation | 26-12 |

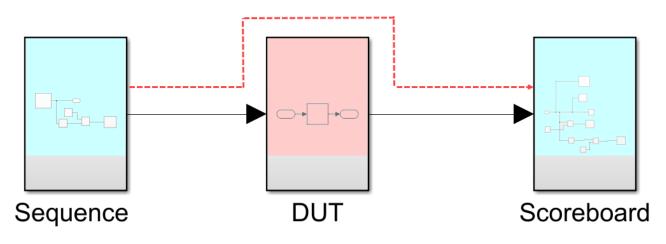

## **UVM Component Generation**

## 27

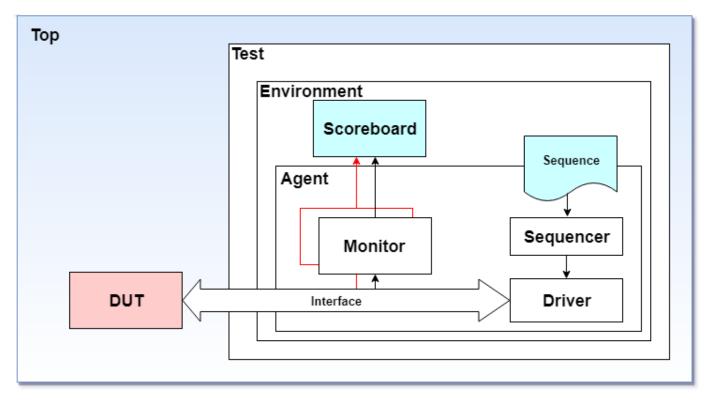

| UVM Component Generation Overview         UVM Component Generation Overview         Prepare Simulink Model for UVM Component Generation         Generated UVM Structure         Generated Files and Folder Structure         Supported Simulink Data Types         Limitations | 27-2<br>27-2<br>27-2<br>27-3<br>27-4<br>27-5<br>27-6 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Use Tunable Parameters to Generalize UVM Simulation                                                                                                                                                                                                                            | 27-7                                                 |

| Tunable Parameters in Sequence Subsystem                                                                                                                                                                                                                                       | 27-8                                                 |

| Prepare Sequence for UVM Generation With Tunable Parameters                                                                                                                                                                                                                    | 27-8                                                 |

| Generate UVM Sequence                                                                                                                                                                                                                                                          | 27-8                                                 |

| Control Sequence Parameters in UVM Simulation                                                                                                                                                                                                                                  | 27-9                                                 |

| Tunable Parameters in Scoreboard Subsystem                                                                                                                                                                                                                                     | 27-10                                                |

| Prepare Scoreboard for UVM Generation with Tunable Parameters                                                                                                                                                                                                                  | 27-10                                                |

| Generate UVM Scoreboard                                                                                                                                                                                                                                                        | 27-10                                                |

| Control Scoreboard Parameters in UVM Simulation                                                                                                                                                                                                                                | 27-11                                                |

## SystemVerilog DPI Component Generation

## **DPI Component Generation for MATLAB Function**

## 28

| DPI Component Generation with MATLAB |  |  |  |

|--------------------------------------|--|--|--|

| Supported MATLAB Data Types          |  |  |  |

| Generated Shared Library             |  |  |  |

| Generated Test Bench                 |  |  |  |

| Generated Outputs                    |  |  |  |

| Generated SystemVerilog Wrapper      |  |  |  |

| Simulation Considerations            |  |  |  |

| Limitations                          |  |  |  |

| Generate DPI Component Using MATLAB              |   |

|--------------------------------------------------|---|

| Create MATLAB Function and Test Bench            |   |

| Generate SystemVerilog DPI Component             |   |

| Run Generated Test Bench in HDL Simulator        |   |

| Use Generated DPI Functions in SystemVerilog     |   |

| Port Generated Component and Test Bench to Linux | 2 |

## **DPI Component Generation for Simulink Subsystem**

## 30

31

29

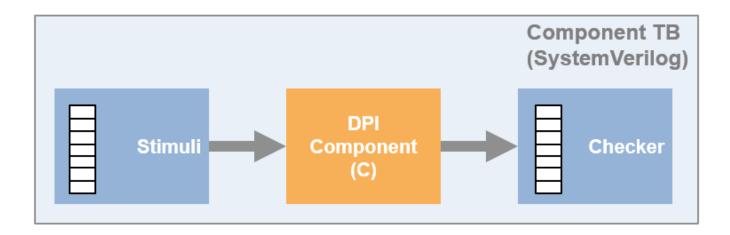

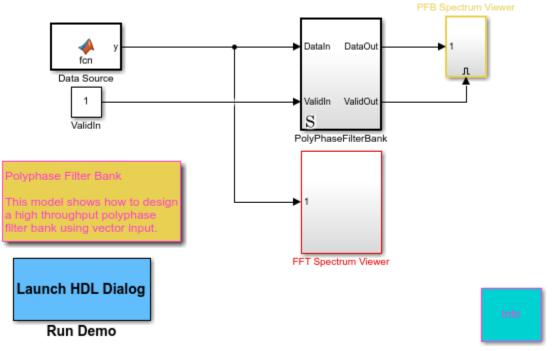

| DPI Component Generation with Simulink         DPI Generation Overview         Supported Simulink Data Types         Generated SystemVerilog Wrapper         Multirate System Behavior         Customization         Limitations | 30-2<br>30-2<br>30-2<br>30-3<br>30-3<br>30-7<br>30-7<br>30-8 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

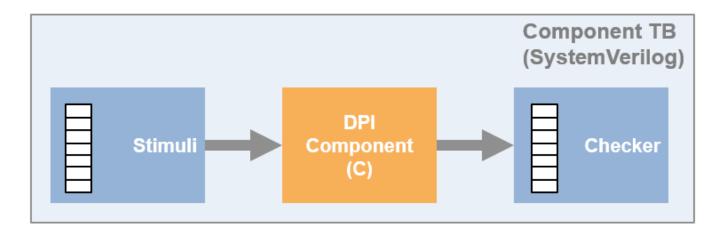

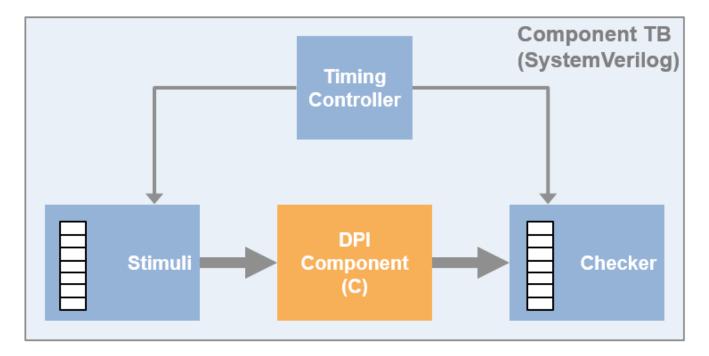

| SystemVerilog DPI Test Benches                                                                                                                                                                                                   | 30-10                                                        |

| Component Test Bench                                                                                                                                                                                                             | 30-10                                                        |

| HDL Code Test Bench                                                                                                                                                                                                              | 30-12                                                        |

## SystemVerilog DPI Component Generation for Simulink

| Generate SystemVerilog DPI Component                          | 31-2  |

|---------------------------------------------------------------|-------|

| Step 1. Select Target                                         | 31-2  |

| Step 2. Select Toolchain                                      | 31-2  |

| Step 3. Enable Test Point Access (Optional)                   | 31-2  |

| Step 4. Configure SystemVerilog Generation Options            | 31-3  |

| Step 5. Generate SystemVerilog DPI Component                  | 31-4  |

| Verify HDL Design With Large Data Set Using SystemVerilog DPI |       |

| Test Bench                                                    | 31-5  |

| Customize Generated SystemVerilog Code                        | 31-10 |

| Set Up Model for Customized Code Generation                   | 31-10 |

| Generate Customized SystemVerilog DPI Component               | 31-11 |

| Verify Generated Component Against Simulink Data              | 31-12 |

| For Mentor Graphics ModelSim and QuestaSim                    | 31-12 |

| For the Cadence Incisive Simulator                            | 31-12 |

| Use Generated DPI Functions in SystemVerilog                  | 31-13 |

| Example                                                       | 31-13 |

| SystemVerilog DPI Component Test Point Access                | 31-14 |

|--------------------------------------------------------------|-------|

| Step 1. Choose Internal Signals                              | 31-14 |

| Step 2. Add Test Points                                      | 31-14 |

| Step 3. Enable Component Interface                           | 31-14 |

| Step 4. Configure Access Function                            | 31-15 |

| Tune Gain Parameter During Simulation                        | 31-16 |

| Step 1. Create a Simple Gain Model                           | 31-16 |

| Step 2. Create Data Object for Gain Parameter                | 31-16 |

| Step 3. Generate SystemVerilog DPI Component                 | 31-18 |

| Step 4. Add Parameter Tuning Code to SystemVerilog File      | 31-18 |

| Step 5. Run Simulation with Parameter Change                 | 31-19 |

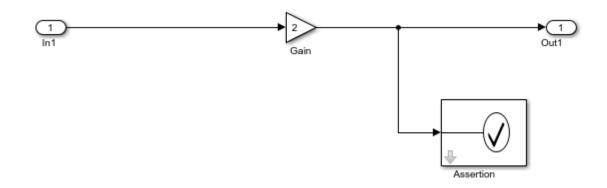

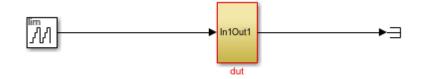

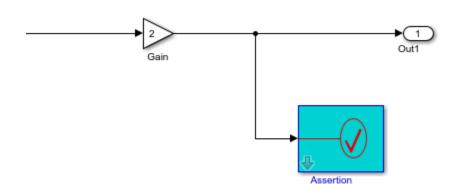

| Generate SystemVerilog Assertions from Simulink Test Bench   | 31-20 |

| Generate Assertions Workflow                                 | 31-20 |

| Trace Generated SystemVerilog Assertions                     | 31-23 |

| Disabling Assertions                                         | 31-24 |

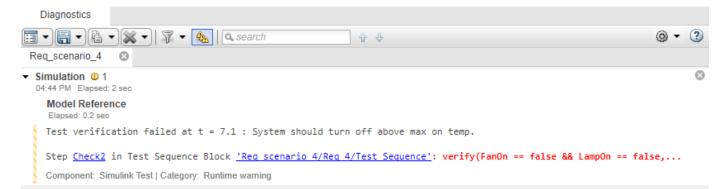

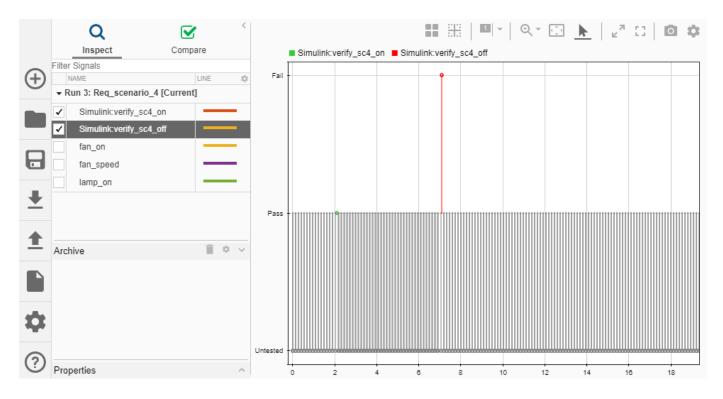

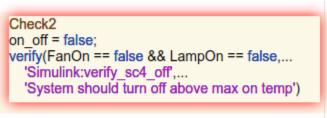

| Generate SystemVerilog DPI Component from verify Statement . | 31-26 |

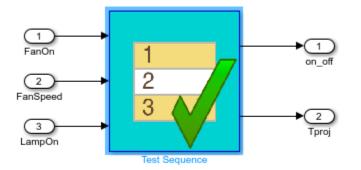

| Create a Simulink Test Sequence                              | 31-26 |

|                                                              | 31-27 |

| Run an HDL Simulation with the Generated Component           | 31-28 |

| Trace Generated SystemVerilog Error Back to Simulink Source  | 31-28 |

| Verbose Mode                                                 | 31-29 |

| Filter Verify Assessments                                    | 31-29 |

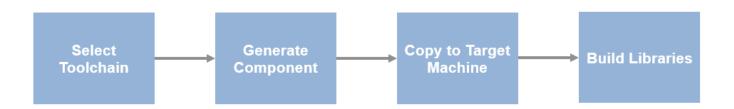

| Generate Cross-Platform DPI Components                       | 31-30 |

| Select Target Toolchain                                      | 31-30 |

| Generate Component                                           | 31-31 |

| Copy to Target Machine                                       | 31-31 |

| Build Libraries                                              | 31-31 |

## Context-Sensitive Help for Generated SystemVerilog DPI Component

## 32

| SystemVerilog DPI Pane                 |  |

|----------------------------------------|--|

| SystemVerilog DPI Overview             |  |

| Customize SystemVerilog generated code |  |

| Source file template:                  |  |

| Generate test bench                    |  |

| Test point access                      |  |

| Fixed-point data type                  |  |

| Connection                             |  |

| Composite Data Type                    |  |

## **HDL Verification with Cosimulation**

## Setup and Run Cosimulation for MATLAB

## Set Up MATLAB-HDL Simulator Connection

#### Start MATLAB Server

Start the MATLAB server as follows:

- **1** Start MATLAB.

- 2 In the MATLAB Command Window, call the hdldaemon function with property name/property value pairs that specify whether the HDL Verifier software is to perform the following tasks:

- Use shared memory or TCP/IP socket communication

- Return time values in seconds or as 64-bit integers

See hdldaemon reference documentation for when and how to specify property name/property value pairs and for more examples of using hdldaemon.

The communication mode that you specify (shared memory or TCP/IP sockets) must match what you specify for the communication mode when you initialize the HDL simulator for use with a MATLAB cosimulation session using the matlabtb or matlabcp function. In addition, if you specify TCP/IP socket mode, the socket port that you specify with hdldaemon and matlabtb or matlabcp must match. See "TCP/IP Socket Ports" on page 10-62 for more information .

The MATLAB server can service multiple simultaneous HDL simulator modules and clients. However, your code must track the I/O associated with each entity or client.

**Note** You cannot begin an HDL Verifier transaction between MATLAB and the HDL simulator from MATLAB. The MATLAB server simply responds to function call requests that it receives from the HDL simulator.

This command sets up socket communication on port 4449, and specifies a 64-bit time resolution format for the MATLAB function's output ports.

hdldaemon('socket',4449,'time','int64')

### **Start HDL Simulator**

Start the HDL simulator directly from MATLAB by calling the HDL Verifier function vsim or nclaunch.

>>vsim

You can call vsim or nclaunch with additional parameters; see the reference pages for details.

You must make sure the HDL simulator executables — also called vsim (ModelSim<sup>®</sup>) and nclaunch (Cadence Incisive<sup>®</sup>) — are on the system path. See your system documentation for instruction on setting environment variables.

**Linux Users** Make sure the HDL simulator executable is still on the system path after the shell is launched from MATLAB. If it is not, make sure the shell startup file does not remove it from the path environment variable.

#### Load an HDL Design for Verification

After you start the HDL simulator from MATLAB with a call to vsim or nclaunch, load an instance of an HDL module for verification or visualization with the function vsimmatlab or hdlsimmatlab. At this point, you should have coded and compiled your HDL model. Issue the function vsimmatlab or hdlsimmatlab for each instance of an entity or module in your model that you want to cosimulate. For example (for use with Incisive<sup>®</sup>):

hdlsimmatlab work.osc\_top

This command loads the HDL Verifier library, opens a simulation workspace for osc\_top, and display a series of messages in the HDL simulator command window as the simulator loads the entity (see example for remaining code).

## **Run MATLAB-HDL Cosimulation**

#### In this section...

"Process for Running MATLAB Cosimulation" on page 1-4

"Check MATLAB Cosimulation Server's Link Status" on page 1-4

"Run Cosimulation" on page 1-4

"Apply Stimuli to Cosimulation Session with force Command" on page 1-7

"Restart Simulation" on page 1-8

"Stop Simulation" on page 1-8

#### **Process for Running MATLAB Cosimulation**

To start and control the execution of a simulation in the MATLAB environment, perform the following steps:

- 1 "Check MATLAB Cosimulation Server's Link Status" on page 1-4

- 2 "Run Cosimulation" on page 1-4

- 3 "Apply Stimuli to Cosimulation Session with force Command" on page 1-7

- 4 "Restart Simulation" on page 1-8 (if applicable).

#### **Check MATLAB Cosimulation Server's Link Status**

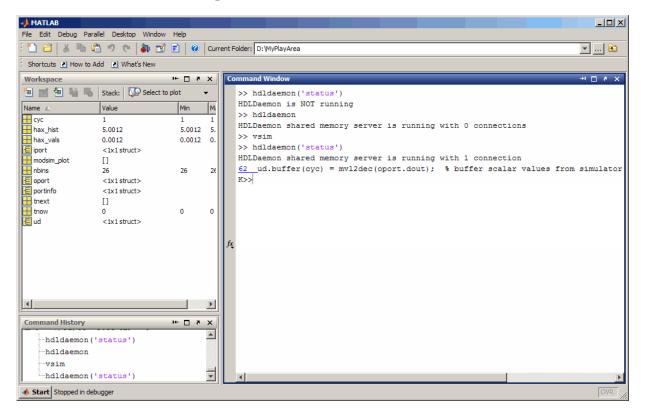

The first step to starting an HDL simulator and MATLAB test bench or component function session is to check the link status of the MATLAB server. Is the server running? If the server is running, what mode of communication and, if applicable, what TCP/IP socket port is the server using for its links? You can retrieve this information by using the MATLAB function hdldaemon with the 'status' option. For example:

hdldaemon('status')

The function displays a message that indicates whether the server is running and, if it is running, the number of connections it is handling. For example:

HDLDaemon socket server is running on port 4449 with 0 connections

If the server is not running, the message reads

HDLDaemon is NOT running

See the Options: Inputs section in the hdldaemon reference documentation for information on determining the mode of communication and the TCP/IP socket in use.

#### **Run Cosimulation**

You can run a cosimulation session using both the MATLAB and HDL simulator GUIs (typical) or, to reduce memory demand, you can run the cosimulation using the command line interface (CLI) or in batch mode.

• "Cosimulation with MATLAB Using the HDL Simulator GUI" on page 1-5

- "Cosimulation with MATLAB Using the Command Line Interface (CLI)" on page 1-6

- "Cosimulation with MATLAB Using Batch Mode" on page 1-7

#### Cosimulation with MATLAB Using the HDL Simulator GUI

These steps describe a typical sequence for running a simulation interactively from the main HDL simulator window:

**1** Set breakpoints in the HDL and MATLAB code to verify and analyze simulation progress.

How you set breakpoints in the HDL simulator will vary depending on what simulator application you are using.

In MATLAB, there are several ways you can set breakpoints; for example, by using the **Set/Clear Breakpoint** button on the toolbar.

2 Issue matlabtb command at the HDL simulator prompt.

When you begin a specific test bench or component session, you specify parameters that identify the following information:

- The mode and, if applicable, TCP/IP data for connecting to a MATLAB server (see matlabtb reference)

- The MATLAB function that is associated with and executes on behalf of the HDL instance. See "Bind HDL Module Component to MATLAB Test Bench Function" on page 2-15.

- Timing specifications and other control data that specifies when the module's MATLAB function is to be called. See "Schedule Options for a Test Bench Session" on page 2-16.

For example:

hdlsim> matlabtb osc\_top -sensitivity /osc\_top/sine\_out

-socket 4448 -mfunc hosctb

**3** Start the simulation by entering the HDL simulator run command.

The run command offers a variety of options for applying control over how a simulation runs (refer to your HDL simulator documentation for details). For example, you can specify that a simulation run for several time steps.

The following command instructs the HDL simulator to run the loaded simulation for 50000 time steps:

run 50000

4 Step through the simulation and examine values.

How you step through the simulation in the HDL simulator will vary depending on what simulator application you are using.

In MATLAB, there are several ways you can step through code; for example, by clicking the **Step** toolbar button.

- **5** When you block execution of the MATLAB function, the HDL simulator also blocks and remains blocked until you clear all breakpoints in the function's code.

- **6** Resume the simulation, as desired.

How you resume the simulation in the HDL simulator will vary depending on what simulator application you are using.

In MATLAB, there are several ways you can resume the simulation; for example, by clicking the **Continue** toolbar button.

The following HDL simulator command resumes a simulation:

run -continue

For more information on HDL simulator and MATLAB debugging features, see the HDL simulator documentation and MATLAB online help or documentation.

#### Cosimulation with MATLAB Using the Command Line Interface (CLI)

Running your cosimulation session using the command-line interface allows you to interact with the HDL simulator during cosimulation, which can be helpful for debugging.

To use the CLI, specify "CLI" as the property value for the run mode parameter of the HDL Verifier HDL simulator launch command.

The Tcl command you build to pass to the HDL simulator launch command must contain the run command or no cosimulation will take place.

**Caution** Close the terminal window by entering quit -f at the command prompt. Do not close the terminal window by clicking the "X" in the upper right-hand corner. This causes a memory-type error to be issued from the system. This is not a bug with HDL Verifier but just the way the HDL simulator behaves in this context.

You can type CTRL+C to interrupt and terminate the simulation in the HDL simulator but this action also causes the memory-type error to be displayed.

#### Specify CLI mode with nclaunch (Cadence Incisive)

Issue the nclaunch command with "CLI" as the runmode property value, as follows (example entered into the MATLAB editor):

nclaunch('tclstart',tclcmd,'runmode','CLI');

#### Specify CLI mode with vsim (Mentor Graphics ModelSim)

Issue the vsim command with "CLI" as the runmode property value, as follows (example entered into the MATLAB editor):

```

tclcmd = { ['cd ',unixprojdir],...

'vlib work',... %create library (if applicable)

'force /osc_top/clk_enable 1 0',...

```

```

'force /osc_top/reset 1 0, 0 120 ns',...

'force /osc_top/clk 1 0 ns, 0 40 ns -r 80ns',...

};

```

```

vsim('tclstart',tclcmd,'runmode','CLI');

```

#### **Cosimulation with MATLAB Using Batch Mode**

Running your cosimulation session in batch mode allows you to keep the process in the background, reducing demand on memory by disengaging the GUI.

To use the batch mode, specify "Batch" as the property value for the run mode parameter of the HDL Verifier HDL simulator launch command. After you issue the HDL Verifier HDL simulator launch command with batch mode specified, start the simulation in Simulink<sup>®</sup>. To stop the HDL simulator before the simulation is completed, issue the breakHdlSim command.

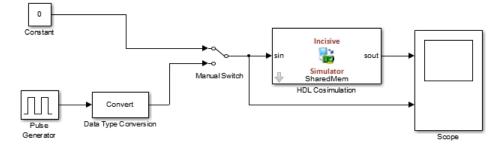

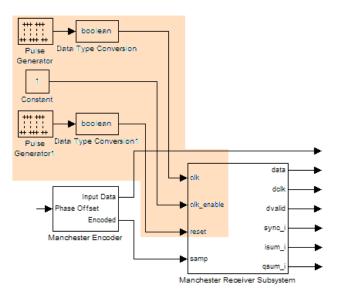

#### Specify Batch mode with nclaunch (Cadence Incisive)

Issue the nclaunch command with "Batch" as the runmode parameter, as follows:

```

nclaunch('tclstart',manchestercmds,'runmode','Batch')

```

You can also set runmode to 'Batch with Xterm', which starts the HDL simulator in the background but shows the session in an Xterm.

#### Specify Batch mode with vsim (Mentor Graphics ModelSim)

On Windows<sup>®</sup>, specifying batch mode causes ModelSim to be run in a non-interactive command window. On Linux<sup>®</sup>, specifying batch mode causes ModelSim to be run in the background with no window.

Issue the vsim command with 'Batch' as the runmode parameter, as follows:

```

>> vsim('tclstart',manchestercmds,'runmode','Batch')

```

#### Apply Stimuli to Cosimulation Session with force Command

After you establish a connection between the HDL simulator and MATLAB, you can then apply stimuli to the test bench or component cosimulation environment. One way of applying stimuli is through the iport parameter of the linked MATLAB function. This parameter forces signal values by deposit.

Other ways to apply stimuli include issuing force commands in the HDL simulator main window (for ModelSim, you can also use the **Edit** > **Clock** option in the **ModelSim Signals** window).

For example, consider the following sequence of force commands:

• Incisive

```

force osc_top.clk_enable 1 -after Ons

force osc_top.reset 0 -after Ons 1 -after 40ns 0 -after 120ns

force osc_top.clk 1 -after Ons 0 -after 40ns -repeat 80ns

```

ModelSim

```

VSIM n> force clk 0 0 ns, 1 5 ns -repeat 10 ns

VSIM n> force clk_en 1 0

VSIM n> force reset 0 0

```

These commands drive the following signals:

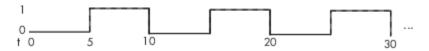

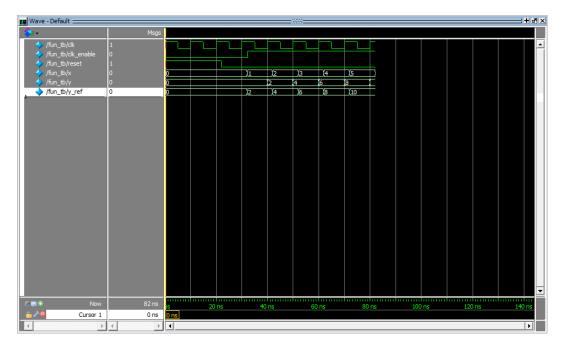

• The clk signal to 0 at 0 nanoseconds after the current simulation time and to 1 at 5 nanoseconds after the current HDL simulation time. This cycle repeats starting at 10 nanoseconds after the current simulation time, causing transitions from 1 to 0 and 0 to 1 every 5 nanoseconds, as the following diagram shows.

For example,

force /foobar/clk 0 0, 1 5 -repeat 10

- The clk\_en signal to 1 at 0 nanoseconds after the current simulation time.

- The reset signal to 0 at 0 nanoseconds after the current simulation time.

#### Incisive Users: Using HDL to Code Clock Signals Instead of the force Command

You should consider using HDL to code clock signals as **force** is a lower performance solution in the current version of Cadence Incisive simulators.

The following are ways that a periodic force might be introduced:

- Via the Clock pane in the HDL Cosimulation block

- Via pre/post Tcl commands in the HDL Cosimulation block

- Via a user-input Tcl script to ncsim

All three approaches may lead to performance degradation.

#### **Restart Simulation**

Because the HDL simulator issues the service requests during a MATLAB cosimulation session, you must restart the session from the HDL simulator. To restart a session, perform the following steps:

- **1** Make the HDL simulator your active window, if your input focus was not already set to that application.

- 2 Reload HDL design elements and reset the simulation time to zero.

- **3** Reissue the matlabtb or matlabcp command.

**Note** To restart a simulation that is in progress, issue a break command and end the current simulation session before restarting a new session.

#### **Stop Simulation**

When you are ready to stop a test bench or component session, it is best to do so in an orderly way to avoid possible corruption of files and to see that all application tasks shut down cleanly. You should stop a session as follows:

**1** Make the HDL simulator your active window, if your input focus was not already set to that application.

- **2** Halt the simulation. You must quit the simulation at the HDL simulator side or MATLAB may hang until the simulator is quit.

- **3** Close your project.

- 4 Exit the HDL simulator, if you are finished with the application.

- **5** Quit MATLAB, if you are finished with the application. If you want to shut down the server manually, stop the server by calling hdldaemon with the 'kill' option:

```

hdldaemon('kill')

```

For more information on closing HDL simulator sessions, see the HDL simulator documentation.

- "Create a MATLAB Test Bench" on page 2-2

- "Set Up Cosimulation Test Bench" on page 2-13

- "Verify HDL Module with MATLAB Test Bench" on page 2-18

- "Automatic Verification of Generated HDL Code from MATLAB" on page 2-30

## **Create a MATLAB Test Bench**

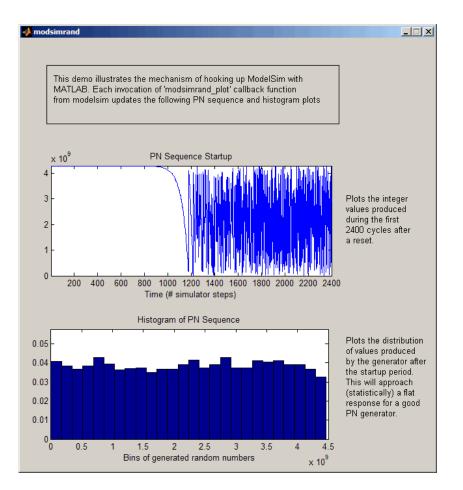

The HDL Verifier software provides a means for verifying HDL modules within the MATLAB environment. You do so by coding an HDL model and a MATLAB function that can share data with the HDL model. This chapter discusses the programming, interfacing, and scheduling conventions for MATLAB test bench functions that communicate with the HDL simulator.

MATLAB test bench functions let you verify the performance of the HDL model, or of components within the model. A test bench function drives values onto signals connected to input ports of an HDL design under test and receives signal values from the output ports of the module.

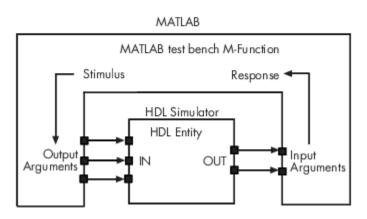

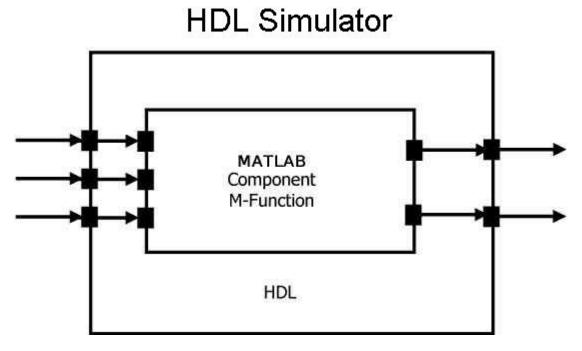

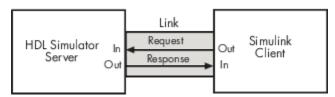

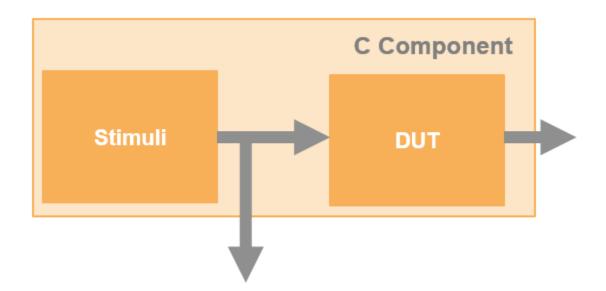

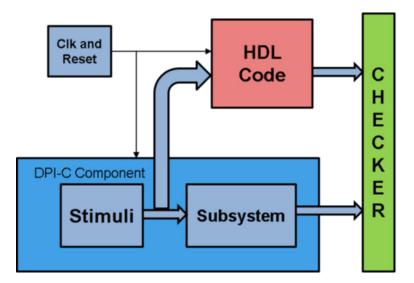

The following figure shows how a MATLAB function wraps around and communicates with the HDL simulator during a test bench simulation session.

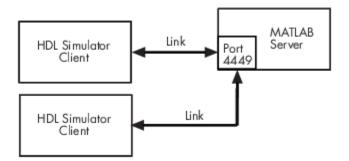

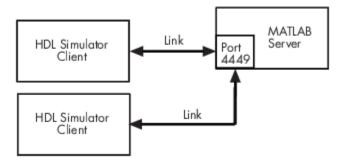

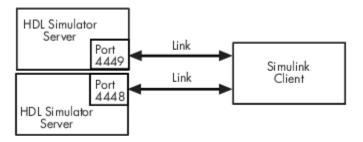

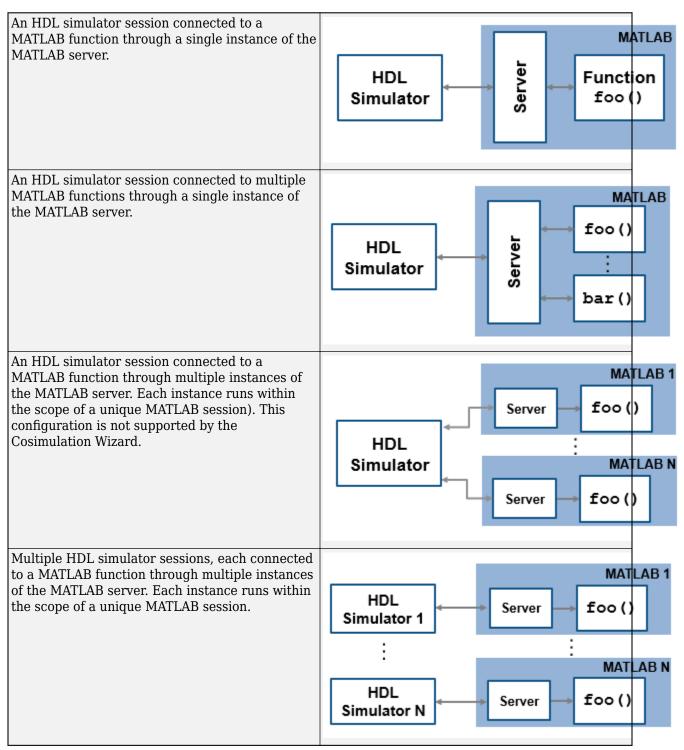

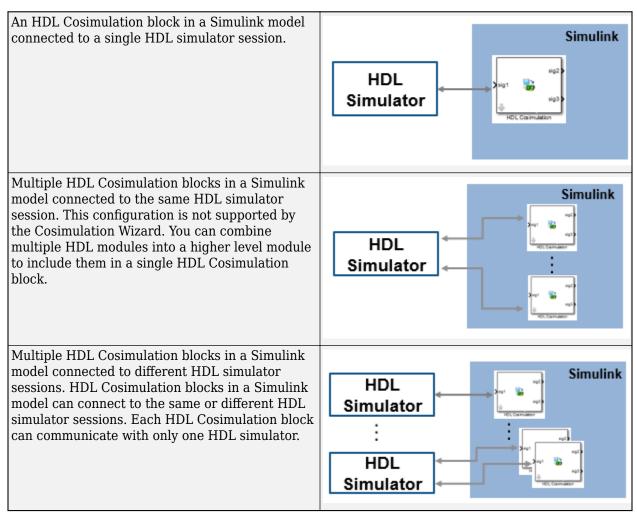

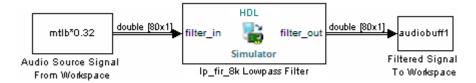

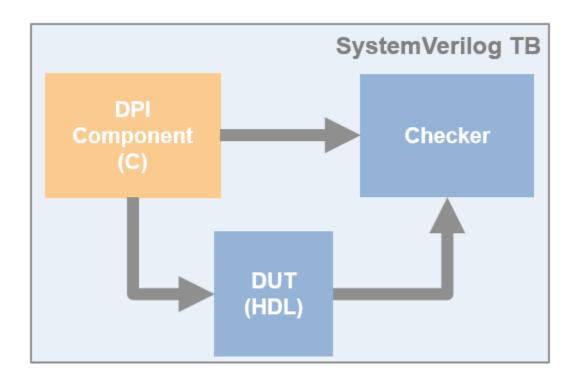

When linked with MATLAB, the HDL simulator functions as the client, with MATLAB as the server. The following figure shows a multiple-client scenario connecting to the server at TCP/IP socket port 4449.

The MATLAB server can service multiple simultaneous HDL simulator sessions and HDL modules. However, you should follow recommended guidelines to help the server track the I/O associated with each module and session. The MATLAB server, which you start with the supplied MATLAB function hdldaemon, waits for connection requests from instances of the HDL simulator running on the same or different computers. When the server receives a request, it executes the specified MATLAB function you have coded to perform tasks on behalf of a module in your HDL design. Parameters that you specify when you start the server indicate whether the server establishes shared memory or TCP/IP socket communication links.

Refer to "Cosimulation Configurations" on page 10-2 for valid machine configurations.

**Note** The programming, interfacing, and scheduling conventions for test bench functions and component functions are virtually identical. For the most part, the same procedures apply to both types of functions.

Follow these workflow steps to create a MATLAB test bench session for cosimulation with the HDL simulator.

- **1** "Write HDL Modules for MATLAB Test Bench" on page 2-3

- 2 "Write a Test Bench Function" on page 2-6

- **3** "Set Up MATLAB-HDL Simulator Connection" on page 1-2

- 4 "Place Test Bench on MATLAB Search Path" on page 2-13

- **5** "Bind Test Bench Function Calls With matlabtb" on page 2-13

- **6** "Schedule Options for a Test Bench Session" on page 2-16

- 7 Set breakpoints for interactive HDL debug (optional).

- 8 "Run MATLAB-HDL Cosimulation" on page 1-4

#### Write HDL Modules for MATLAB Test Bench

- "Coding HDL Modules for Verification with MATLAB" on page 2-3

- "Choose HDL Module Name for Use with MATLAB Test Bench" on page 2-3

- "Specify Port Direction Modes in HDL Module for Use with Test Bench" on page 2-4

- "Specify Port Data Types in HDL Modules for Use with Test Bench" on page 2-4

- "Compile and Elaborate HDL Design for Use with Test Bench" on page 2-5

- "Sample VHDL Entity Definition" on page 2-6

#### Coding HDL Modules for Verification with MATLAB

The most basic element of communication in the HDL Verifier interface is the HDL module. The interface passes all data between the HDL simulator and MATLAB as port data. The HDL Verifier software works with any existing HDL module. However, when you code an HDL module that is targeted for MATLAB verification, you should consider its name, the types of data to be shared between the two environments, and the direction modes.

#### Choose HDL Module Name for Use with MATLAB Test Bench

Although not required, when naming the HDL module, consider choosing a name that also can be used as a MATLAB function name. (Generally, naming rules for VHDL<sup>®</sup> or Verilog<sup>®</sup> and MATLAB are compatible.) By default, HDL Verifier software assumes that an HDL module and its simulation function share the same name. See "Bind Test Bench Function Calls With matlabtb" on page 2-13.

For details on MATLAB function-naming guidelines, see "MATLAB Programming Tips" on files and file names in the MATLAB documentation.

#### Specify Port Direction Modes in HDL Module for Use with Test Bench

In your module statement, you must specify each port with a direction mode (input, output, or bidirectional). The following table defines these three modes.

| Use VHDL Mode | Use Verilog<br>Mode | For Ports That                                                                            |

|---------------|---------------------|-------------------------------------------------------------------------------------------|

| IN            | input               | Represent signals that can be driven by a MATLAB function                                 |

| OUT           | output              | Represent signal values that are passed to a MATLAB function                              |

| INOUT         | inout               | Represent bidirectional signals that can be driven by or pass values to a MATLAB function |

#### Specify Port Data Types in HDL Modules for Use with Test Bench

This section describes how to specify data types compatible with MATLAB for ports in your HDL modules. For details on how the HDL Verifier interface converts data types for the MATLAB environment, see "Supported Data Types" on page 10-37.

**Note** If you use unsupported types, the HDL Verifier software issues a warning and ignores the port at run time. For example, if you define your interface with five ports, one of which is a VHDL access port, at run time, then the interface displays a warning and your code sees only four ports.

#### Port Data Types for VHDL Entities

In your entity statement, you must define each port that you plan to test with MATLAB with a VHDL data type that is supported by the HDL Verifier software. The interface can convert scalar and array data of the following VHDL types to comparable MATLAB types:

- STD\_LOGIC, STD\_ULOGIC, BIT, STD\_LOGIC\_VECTOR, STD\_ULOGIC\_VECTOR, and BIT\_VECTOR

- INTEGER and NATURAL

- REAL

- TIME

- Enumerated types, including user-defined enumerated types and CHARACTER

The interface also supports all subtypes and arrays of the preceding types.

**Note** The HDL Verifier software does not support VHDL extended identifiers for the following components:

- Port and signal names used in cosimulation

- Enum literals when used as array indices of port and signal names used in cosimulation

However, the software does support basic identifiers for VHDL.

#### Port Data Types for Verilog Modules

In your module definition, you must define each port that you plan to test with MATLAB with a Verilog port data type that is supported by the HDL Verifier software. The interface can convert data of the following Verilog port types to comparable MATLAB types:

- reg

- integer

- wire

**Note** HDL Verifier software does not support Verilog escaped identifiers for port and signal names used in cosimulation. However, it does support simple identifiers for Verilog.

#### Compile and Elaborate HDL Design for Use with Test Bench

After you create or edit your HDL source files, use the HDL simulator compiler to compile and debug the code.

#### Compilation for ModelSim

You have the option of invoking the compiler from menus in the ModelSim graphic interface or from the command line with the vcom command. The following sequence of ModelSim commands creates and maps the design library work and compiles the VHDL file modsimrand.vhd:

ModelSim> vlib work ModelSim> vmap work work ModelSim> vcom modsimrand.vhd

The following sequence of ModelSim commands creates and maps the design library work and compiles the Verilog file test.v:

ModelSim> vlib work ModelSim> vmap work work ModelSim> vlog test.v

**Note** You should provide read/write access to the signals that are connecting to the MATLAB session for cosimulation. For higher performance, you want to provide access only to those signals used in cosimulation. You can check read/write access through the HDL simulator—see HDL simulator documentation for details.

#### **Compilation for Incisive**

The Cadence Incisive simulator allows for 1-step and 3-step processes for HDL compilation, elaboration, and simulation. The following Cadence Incisive simulator command compiles the Verilog file test.v:

sh> ncvlog -64bit test.v

The following Cadence Incisive simulator command compiles and elaborates the Verilog design test.v, and then loads it for simulation, in a single step:

sh> ncverilog -64bit +gui +access+rwc +linedebug test.v

The following sequence of Cadence Incisive simulator commands performs all the same processes in multiple steps:

```

sh> ncvlog -64bit -linedebug test.v

sh> ncelab -64bit -access +rwc test

sh> ncsim test

```

**Note** You should provide read/write access to the signals that are connecting to the MATLAB session for cosimulation. The previous example shows how to provide read/write access to all signals in your design. For higher performance, you want to provide access only to those signals used in cosimulation. See the description of the +access flag to ncverilog and the -access argument to ncelab for details.

For more examples, see the HDL Verifier tutorials and demos. For details on using the HDL compiler, see the simulator documentation.

#### Sample VHDL Entity Definition

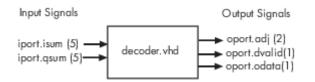

This sample VHDL code fragment defines the entity decoder. By default, the entity is associated with MATLAB test bench function decoder.

The keyword PORT marks the start of the entity's port clause, which defines two IN ports—isum and qsum—and three OUT ports—adj, dvalid, and odata. The output ports drive signals to MATLAB function input ports for processing. The input ports receive signals from the MATLAB function output ports.

Both input ports are defined as vectors consisting of five standard logic values. The output port adj is also defined as a standard logic vector, but consists of only two values. The output ports dvalid and odata are defined as scalar standard logic ports. For information on how the HDL Verifier interface converts data of standard logic scalar and array types for use in the MATLAB environment, see "Supported Data Types" on page 10-37.

```

ENTITY decoder IS

PORT (

isum : IN std_logic_vector(4 DOWNTO 0);

qsum : IN std_logic_vector(4 DOWNTO 0);

adj : OUT std_logic_vector(1 DOWNTO 0);

dvalid : OUT std_logic;

odata : OUT std_logic);

END decoder ;

```

#### Write a Test Bench Function

#### **Coding MATLAB Cosimulation Functions**

Coding a MATLAB function to verify an HDL module or component requires that you follow specific coding conventions. You must also understand the data type conversions that occur, and program data type conversions for operating on data and returning data to the HDL simulator.

To code a MATLAB function to verify an HDL module or component, perform the following steps:

Learn the syntax for a MATLAB HDL Verifier test bench function. See "Syntax of a Test Bench Function" on page 2-7.

- **2** Understand how HDL Verifier software converts data from the HDL simulator for use in the MATLAB environment. See "Supported Data Types" on page 10-37.

- **3** Choose a name for the MATLAB function. See "Bind HDL Module Component to MATLAB Test Bench Function" on page 2-15.

- **4** Define expected parameters in the function definition line. See "MATLAB Function Syntax and Function Argument Definitions" on page 10-24.

- **5** Determine the types of port data being passed into the function. See "MATLAB Function Syntax and Function Argument Definitions" on page 10-24.

- 6 Extract and, if applicable to the simulation, apply information received in the portinfo structure. See "Gaining Access to and Applying Port Information" on page 10-26.

- 7 Convert data for manipulation in the MATLAB environment, as applicable. See "Converting HDL Data to Send to MATLAB" on page 10-37.

- **8** Convert data that needs to be returned to the HDL simulator. See "Converting Data for Return to the HDL Simulator" on page 10-41.

For more tips, see "Test Bench and Component Function Writing" on page 10-21.

#### Syntax of a Test Bench Function

The syntax of a MATLAB test bench function is

function [iport, tnext] = MyFunctionName(oport, tnow, portinfo)

See the "MATLAB Function Syntax and Function Argument Definitions" on page 10-24 for an explanation of each of the function arguments.

### Sample MATLAB Test Bench Function

This section uses a sample MATLAB function to identify sections of a MATLAB test bench function required by the HDL Verifier software. You can see the full text of the code used in this sample in the section "MATLAB Builder EX Function Example: manchester\_decoder.m" on page 2-10.

**For ModelSim Users** This example uses a VHDL entity and MATLAB Builder<sup>™</sup> EX function code drawn from the decoder portion of the Manchester Receiver example. For the complete VHDL and function code listings, see the following files:

matlabroot\toolbox\edalink\extensions\modelsim\modelsimdemos\vhdl\manchester\decoder.vhd

matlabroot\toolbox\edalink\extensions\modelsim\modelsimdemos\manchester\_decoder.m

As the first step to coding a MATLAB Builder EX test bench function, you must understand how the data modeled in the VHDL entity maps to data in the MATLAB Builder EX environment. The VHDL entity decoder is defined as follows:

```

ENTITY decoder IS

PORT (

isum : IN std_logic_vector(4 DOWNTO 0);

qsum : IN std_logic_vector(4 DOWNTO 0);

adj : OUT std_logic_vector(1 DOWNTO 0);

dvalid : OUT std_logic;

odata : OUT std_logic

);

END decoder ;

```

The following discussion highlights key lines of code in the definition of the manchester\_decoder MATLAB Builder EX function:

## **1** Specify the MATLAB function name and required parameters.

The following code is the function declaration of the manchester\_decoder MATLAB Builder EX function.

function [iport,tnext] = manchester\_decoder(oport,tnow,portinfo)

See "MATLAB Function Syntax and Function Argument Definitions" on page 10-24.

The function declaration performs the following actions:

- Names the function. This declaration names the function manchester\_decoder, which differs from the entity name decoder. Because the names differ, the function name must be specified explicitly later when the entity is initialized for verification with the matlabtb or matlabtbeval function. See "Bind HDL Module Component to MATLAB Test Bench Function" on page 2-15.

- Defines required argument and return parameters. A MATLAB Builder EX test bench function *must* return two parameters, iport and tnext, and pass three arguments, oport, tnow, and portinfo, and *must* appear in the order shown. See "MATLAB Function Syntax and Function Argument Definitions" on page 10-24.

The function outputs must be initialized to empty values, as in the following code example:

tnext = []; iport = struct();

You should initialize the function outputs at the beginning of the function, to follow recommended best practice.

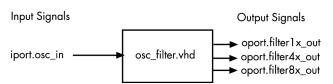

The following figure shows the relationship between the entity's ports and the MATLAB Builder EX function's iport and oport parameters.

For more information on the required MATLAB Builder EX test bench function parameters, see "MATLAB Function Syntax and Function Argument Definitions" on page 10-24.

## 2 Make note of the data types of ports defined for the entity being simulated.

The HDL Verifier software converts HDL data types to comparable MATLAB Builder EX data types and vice versa. As you develop your MATLAB Builder EX function, you must know the types of the data that it receives from the HDL simulator and needs to return to the HDL simulator.

The VHDL entity defined for this example consists of the following ports

## **VHDL Example Port Definitions**

| Port   | Direction | Туре                         | Converts to/<br>Requires<br>Conversion to                                                                                                                                         |

|--------|-----------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| isum   | IN        | STD_LOGIC_VECTOR(4 DOWNTO 0) | A 5-bit column or row<br>vector of characters<br>where each bit maps<br>to a standard logic<br>character literal.                                                                 |

| qsum   | IN        | STD_LOGIC_VECTOR(4 DOWNTO 0) | A 5-bit column or row<br>vector of characters<br>where each bit maps<br>to a standard logic<br>character literal.                                                                 |

| adj    | OUT       | STD_LOGIC_VECTOR(1 DOWNTO 0) | A 2-element column<br>vector of characters.<br>Each character<br>matches a<br>corresponding<br>character literal that<br>represents a logic<br>state and maps to a<br>single bit. |

| dvalid | OUT       | STD_LOGIC                    | A character that<br>matches the<br>character literal<br>representing the<br>logic state.                                                                                          |

| odata  | OUT       | STD_LOGIC                    | A character that<br>matches the<br>character literal<br>representing the<br>logic state.                                                                                          |

For more information on interface data type conversions, see "Supported Data Types" on page 10-37.

## **3** Set up any required timing parameters.

The tnext assignment statement sets up timing parameter tnext such that the simulator calls back the MATLAB Builder EX function every nanosecond.

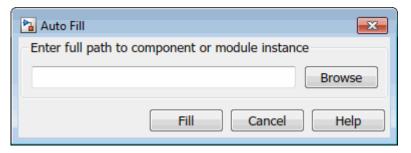

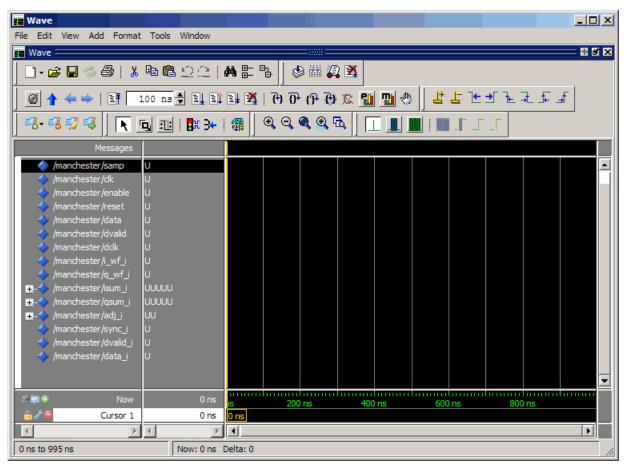

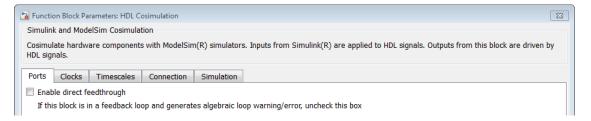

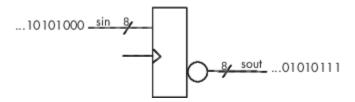

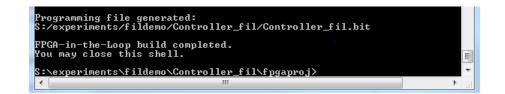

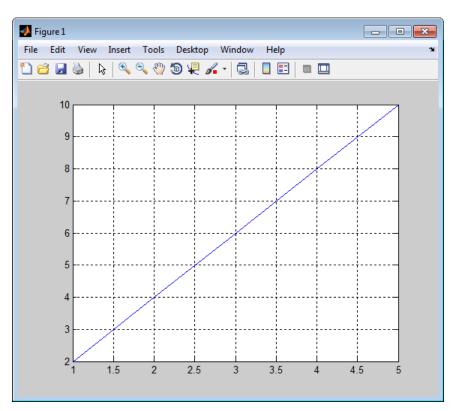

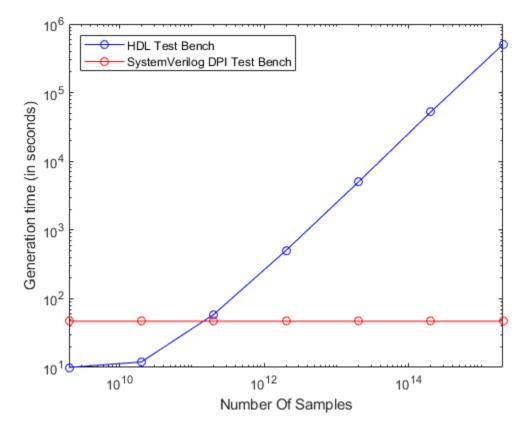

tnext = tnow+1e-9;